# 液体アルゴンTPC用信号読み出し エレクトロニクス 及びファームウェアの開発

岩手大学大学院 総合科学研究科

李沢 祥太

MPGD&Active媒質TPC2020研究会@神戸大学

# 序論 研究目的

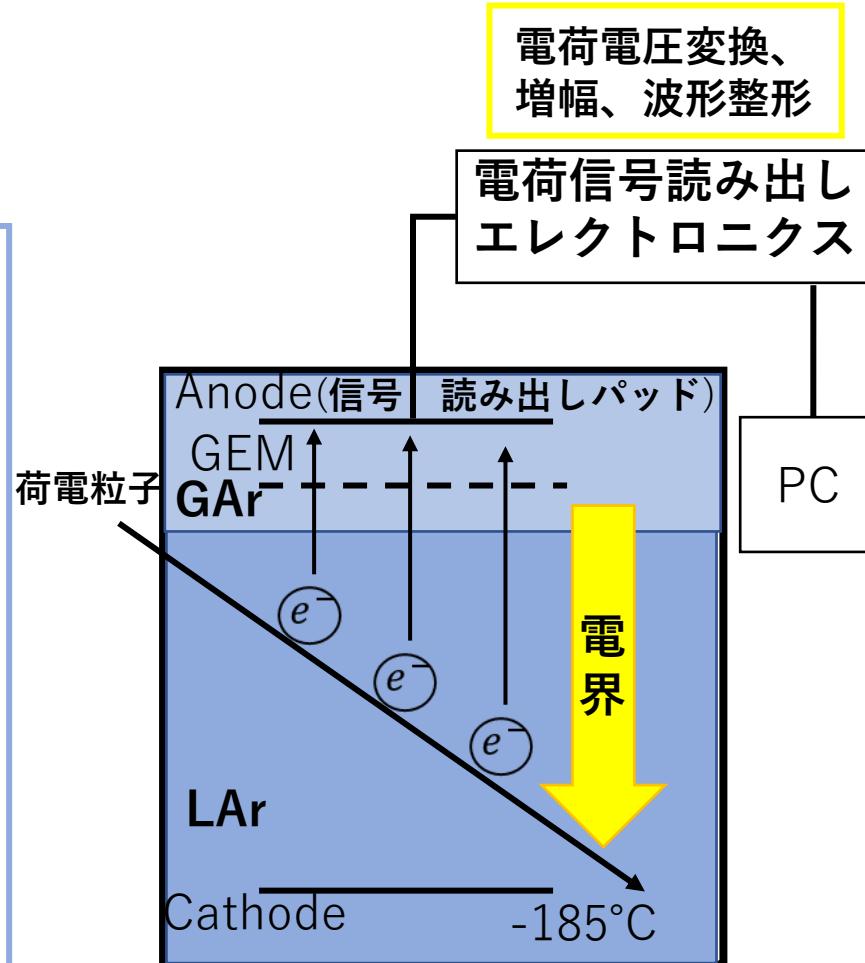

TPC(Time Projection Chamber)を用いて

- 液体アルゴンTPC (LAr-TPC)による、

ニュートリノの性質解明、陽子崩壊探索

- 陰イオンガスTPC ( $\mathrm{N}\mathrm{I}\mu\mathrm{TPC}$ )を用いた暗黒物質探索実験

が計画、進められている。

両TPCで汎用的に用いることが可能である

**ASIC技術に基づく信号読み出しエレクトロニクス**

**LTARS(Low Temperature Analog Readout System)**

を開発した

# 信号読み出しエレクトロニクスへの要求

## 信号読み出しエレクトロニクスの開発目標(LAr-TPC)

- ・高集積

- ・低消費電力

- ・低温環境下での安定動作

(液体アルゴン温度-185°C)

- ・低ノイズ(ENC < 2000 electron)

mip信号をS/N10以上で読み出す

- ・高ゲイン(10mV/fC)

- ・ワイドダイナミックレンジ ( $\pm 1600\text{fC}$ )

最小電離粒子による事象に対し、約50倍の大きさであるシャワー事象を検出したい

液体アルゴンTPC概略図

# 信号読み出しエレクトロニクスへの要求

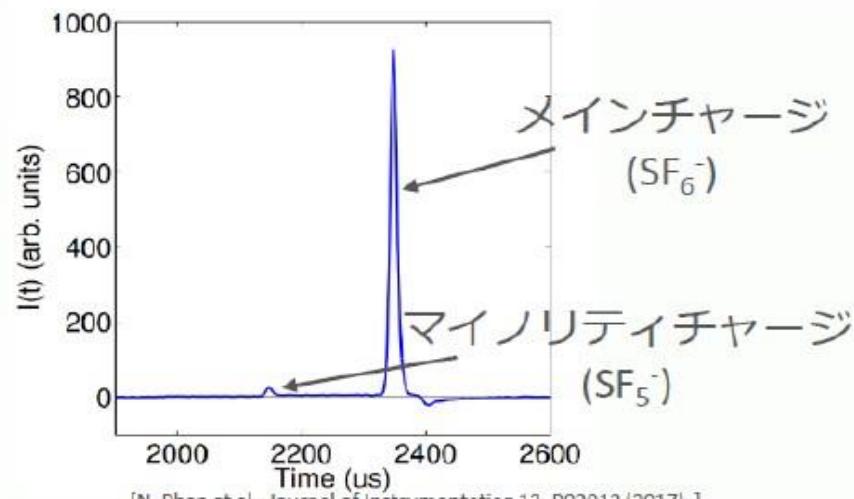

## 暗黒物質探索実験

### 信号読み出しエレクトロニクスの開発目標(NI $\mu$ TPC)

- NI $\mu$ TPCで検出する信号の特徴

1. 陰イオンのドリフト速度が電子に比べて遅い

→時定数が大きい回路が必要

2. メインチャージに対してマイノリティチャージのピークが3%程度である

(生成されるイオンの電荷量が異なる)

→ダイナミックレンジの広い回路が必要である。

- 高集積

- 低消費電力

- 低ノイズ

# 信号読み出しエレクトロニクスへの性能目標

汎用的使用も考慮し、

ゲイン(HG/LG)や時定数(Fast/Slow)の切り替えを搭載したASICの開発

LTARS2018 K06プロジェクトとして

2つのASICを作成

LTARS2018\_K06A → 神戸大で評価

LTARS2018\_K06B → 本発表

[http://openit.kek.jp/project/LTARS2018\\_K06](http://openit.kek.jp/project/LTARS2018_K06)

## LTARS2018 K06B性能目標

| Parameter       | High Gain (HG)                                   | Low Gain (LG)                            |

|-----------------|--------------------------------------------------|------------------------------------------|

| Peaking Time    | $1\ \mu\text{s}$ (Fast), $4\ \mu\text{s}$ (Slow) | ・波形の立ち上がりからピーカまで                         |

| Conversion Gain | $10\ \text{mV/fC}$                               | $0.5\ \text{mV/fC}$                      |

| Dynamic Range   | $\pm 80\ \text{fC}$                              | $\pm 1600\ \text{fC}$                    |

| ENC(electron)   | $< 3000$                                         | $< 62500$<br>・検出器容量 $300\ \text{pF}$ を想定 |

### 試験内容

- ASICの**特性評価試験**

- LAr-TPCでの使用を想定した**低温試験**

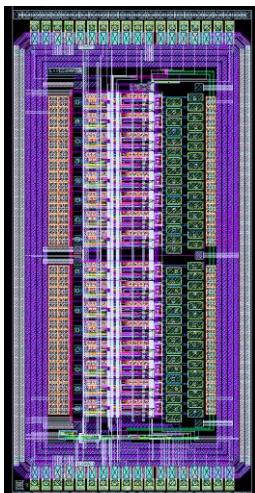

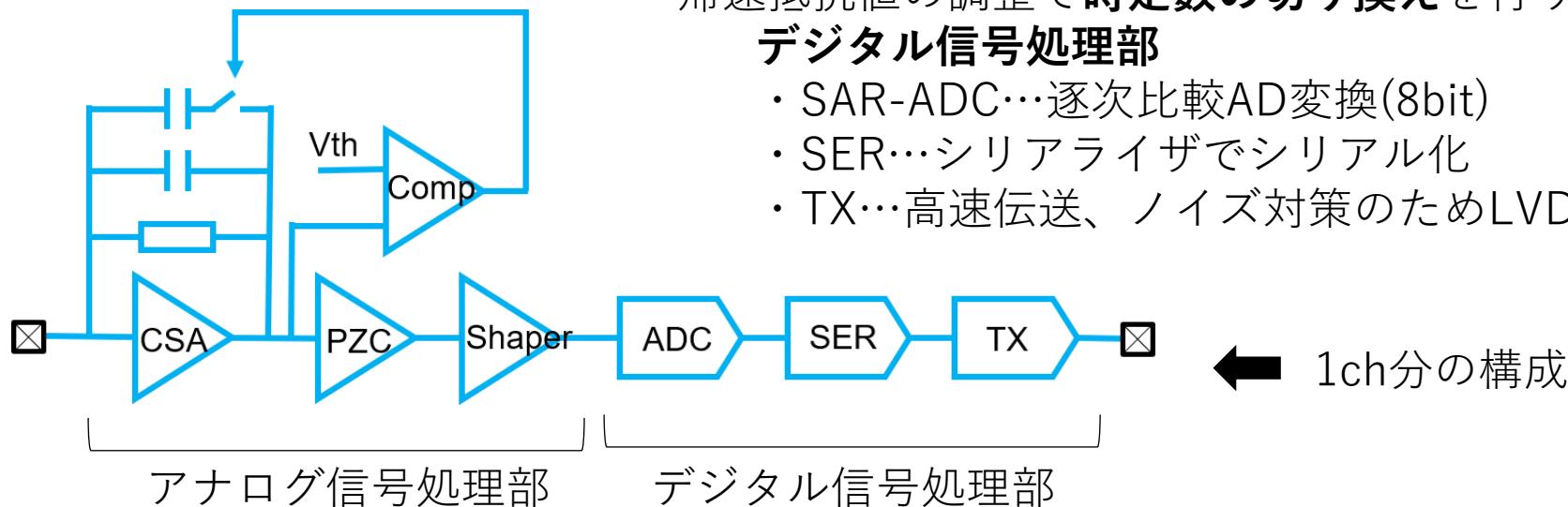

# ASICの回路構成

レイアウト図

## LTARS2018 K06B

### <回路構成>

#### アナログ信号処理部

- ・電荷有感型前置増幅器(CSA)…電荷電圧変換回路

- ・比較器(Comp)…CSAの出力の大きさに応じて

#### ゲインの自動切り替えを行う

- ・ポールゼロキャンセル回路(PZC)…ハイパスフィルタで長い時定数をキャンセル

- ・波形整形回路(Shaper)…波形の増幅、整形

帰還抵抗値の調整で時定数の切り換えを行う

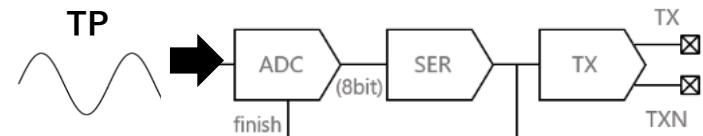

#### デジタル信号処理部

- ・SAR-ADC…逐次比較AD変換(8bit)

- ・SER…シリアルライザでシリアル化

- ・TX…高速伝送、ノイズ対策のためLVDSで伝送

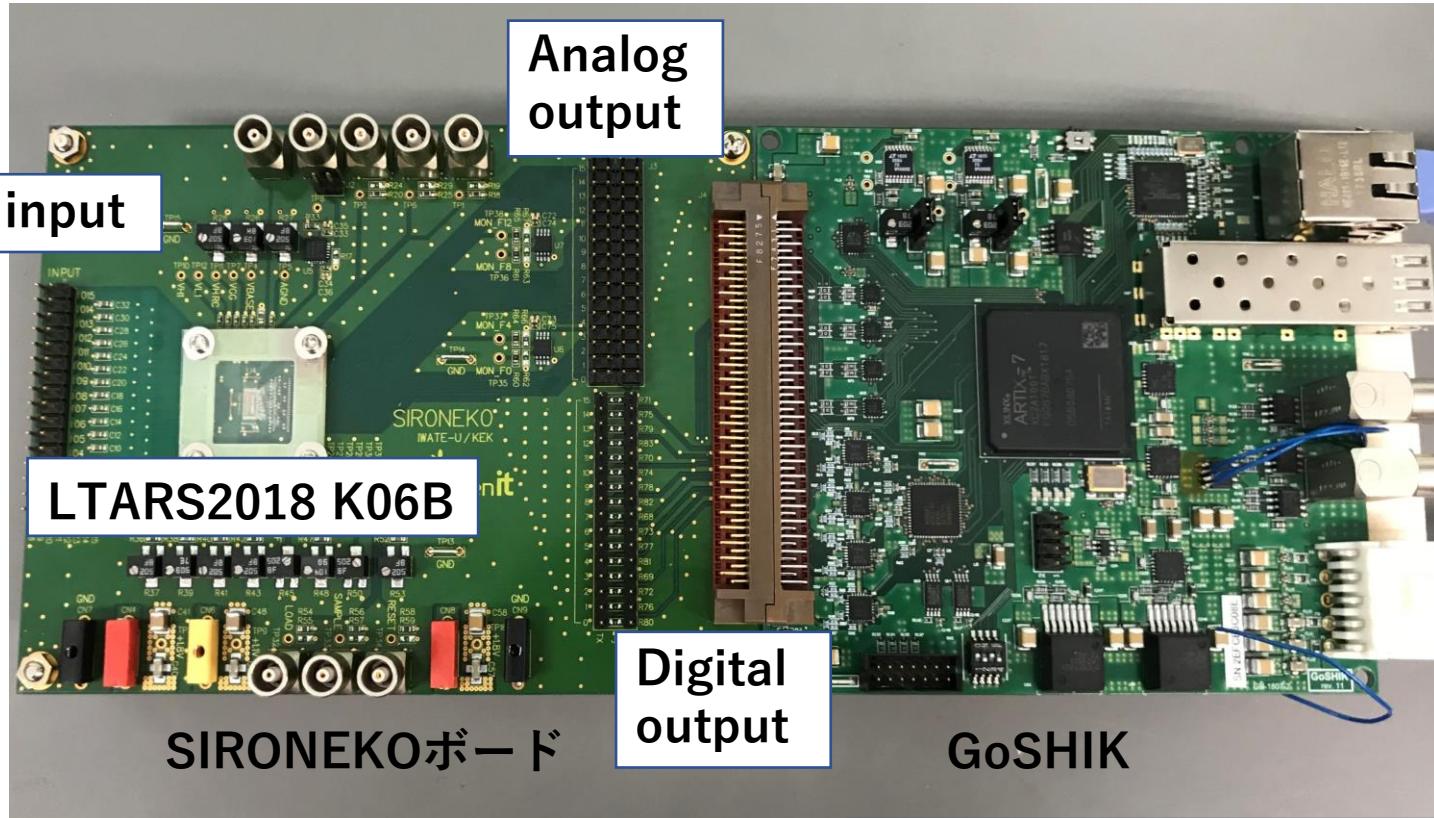

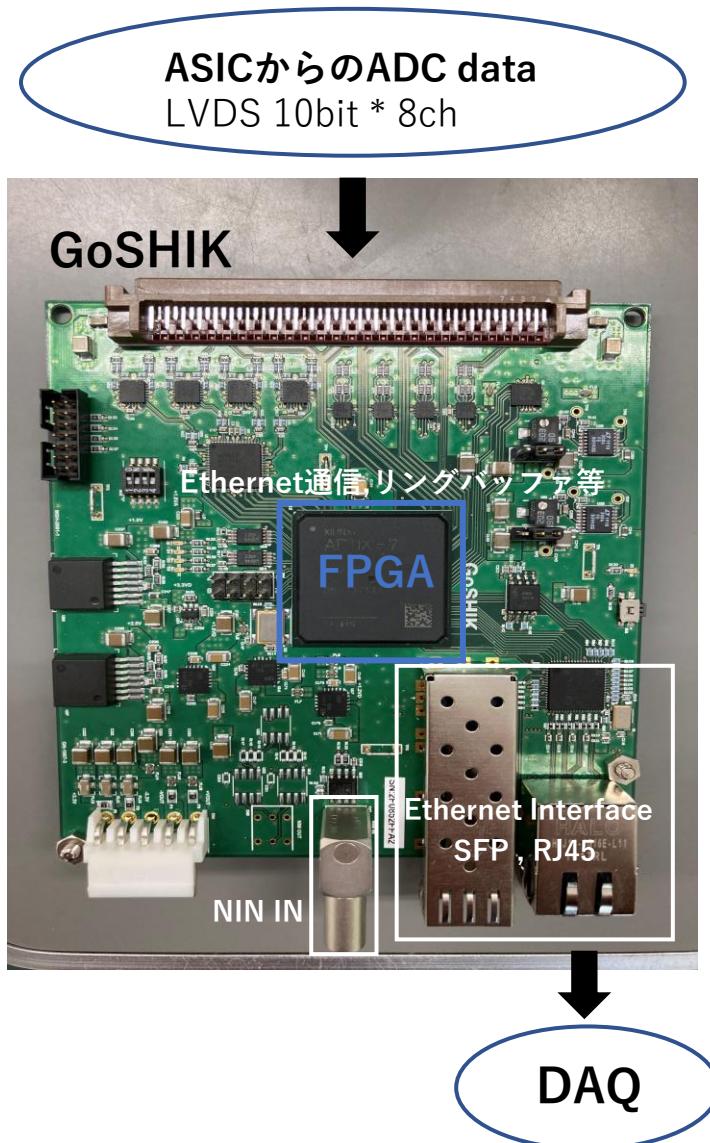

# ASIC特性評価用ボード

## SIRONEKO ボード

- 16 ch

- SIRONEKO ボード input で  $1fC/mV$  の電圧電荷変換

- GoSHIK から Slow Control で ASIC のパラメータ変更可

## GoSHIK(今回はSlow Controlのみ使用)

- FPGA + SiTCP

- 8ch ADC (AD9637)

- 32 ch digital single end I/O

- 8ch LVDS Current DAC

- 8ch Voltage DAC

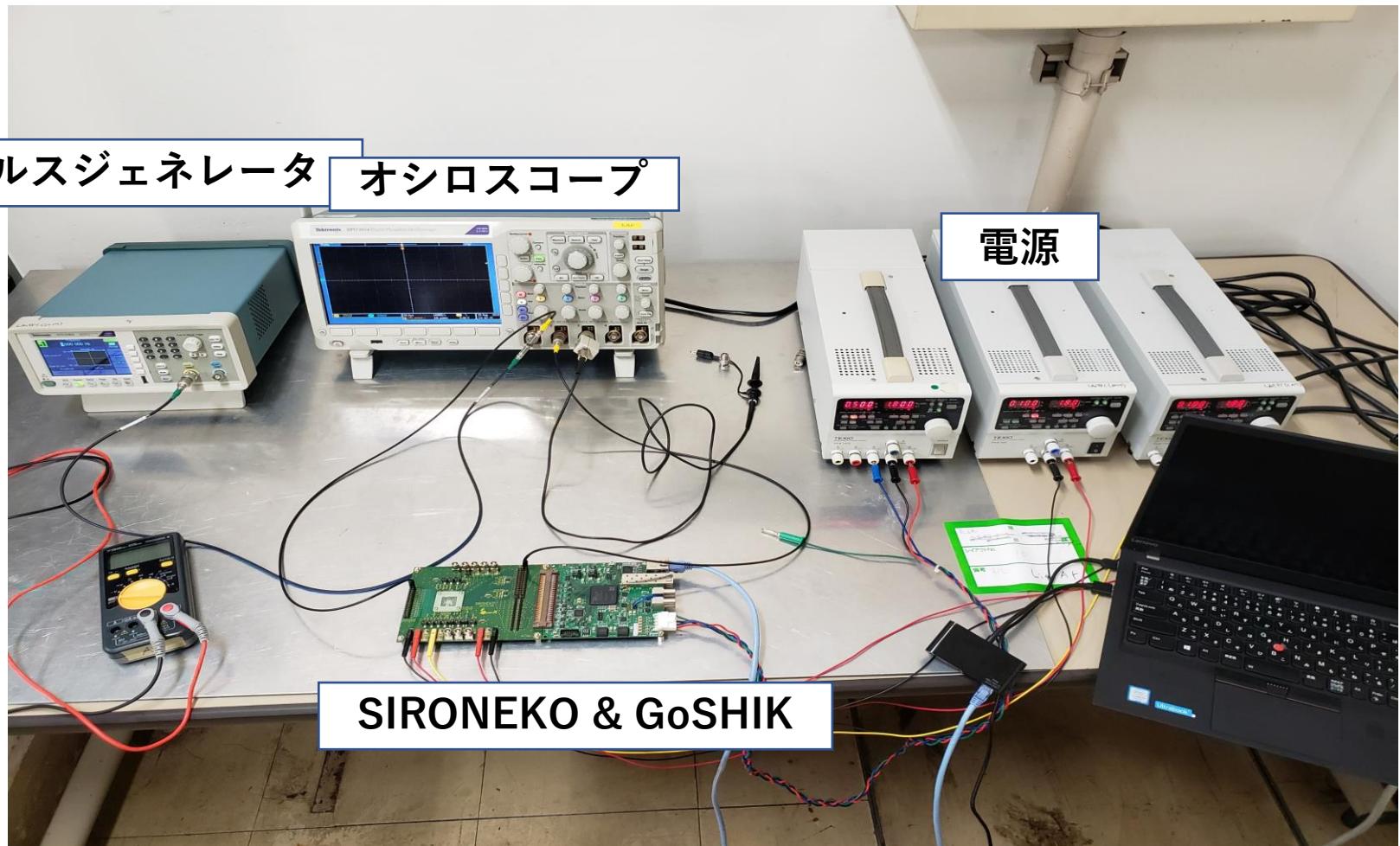

# 特性評価試験セットアップ

- ・パルスジェネレータより、SIRONEKOボードへ

パルス電圧の入力(電圧電荷変換で電荷入力)

- ・オシロスコープで出力のモニター、データ取得

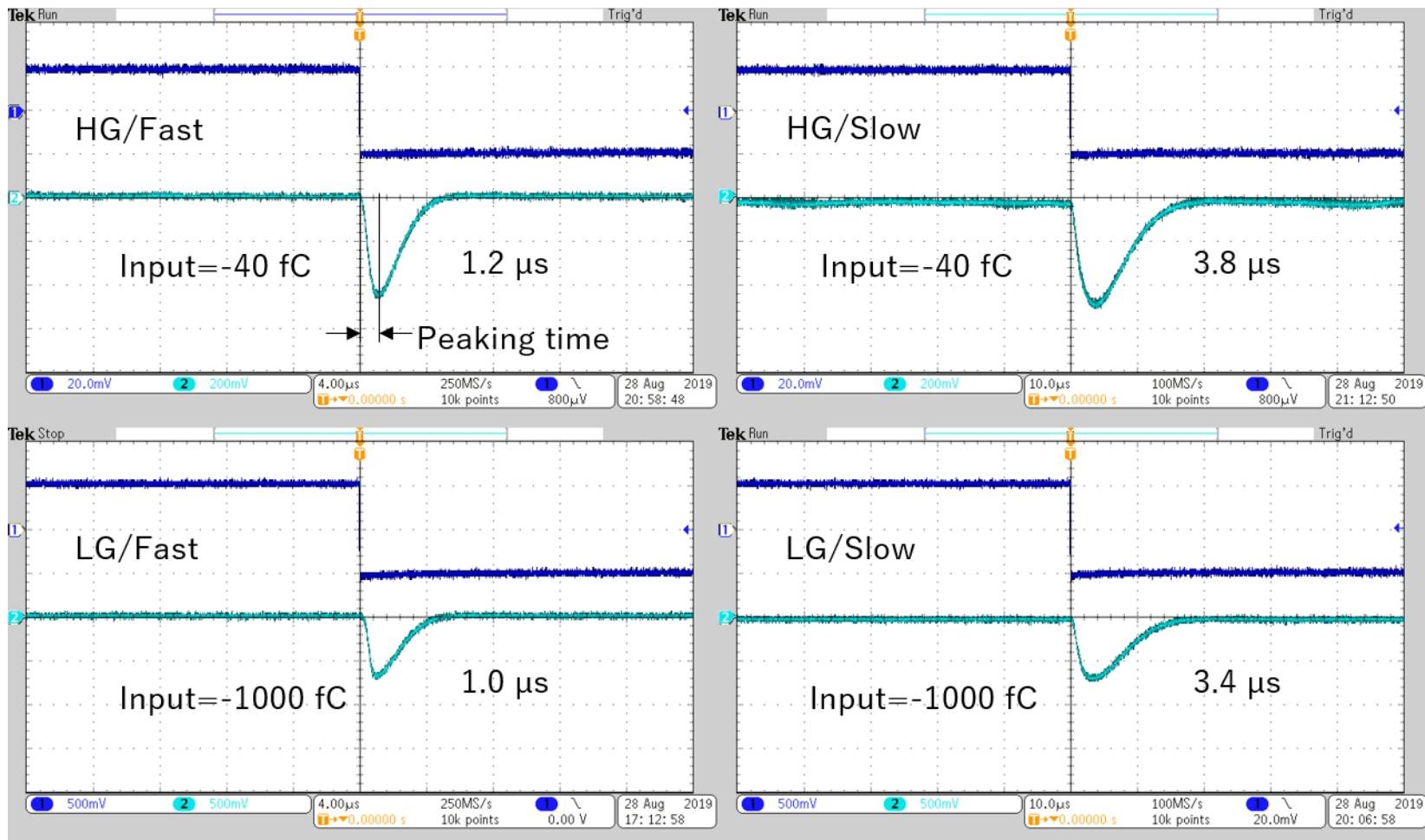

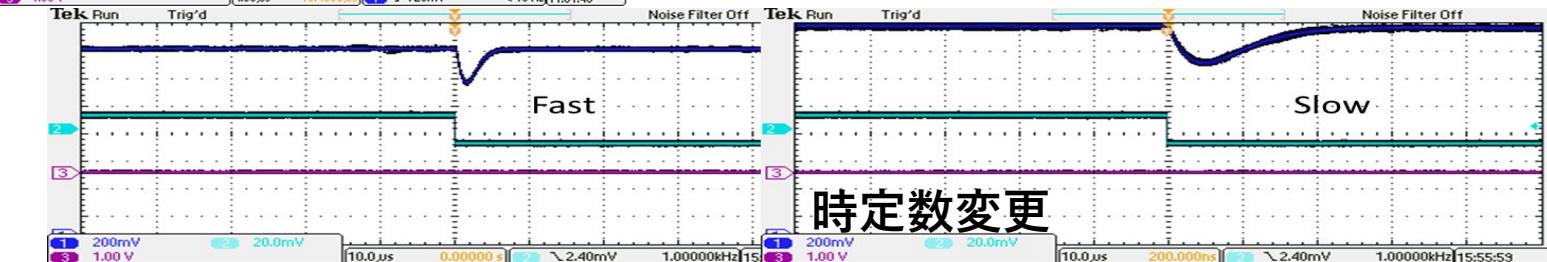

# アナログ出力波形

## 要請値

Fast →  $1\ \mu s$

Slow →  $4\ \mu s$

- HG / LG , Fast / Slow それぞれのモードで波形を取得

- Peaking Timeに関して Fast , Slow 両モードで

要請値に近い値を示している

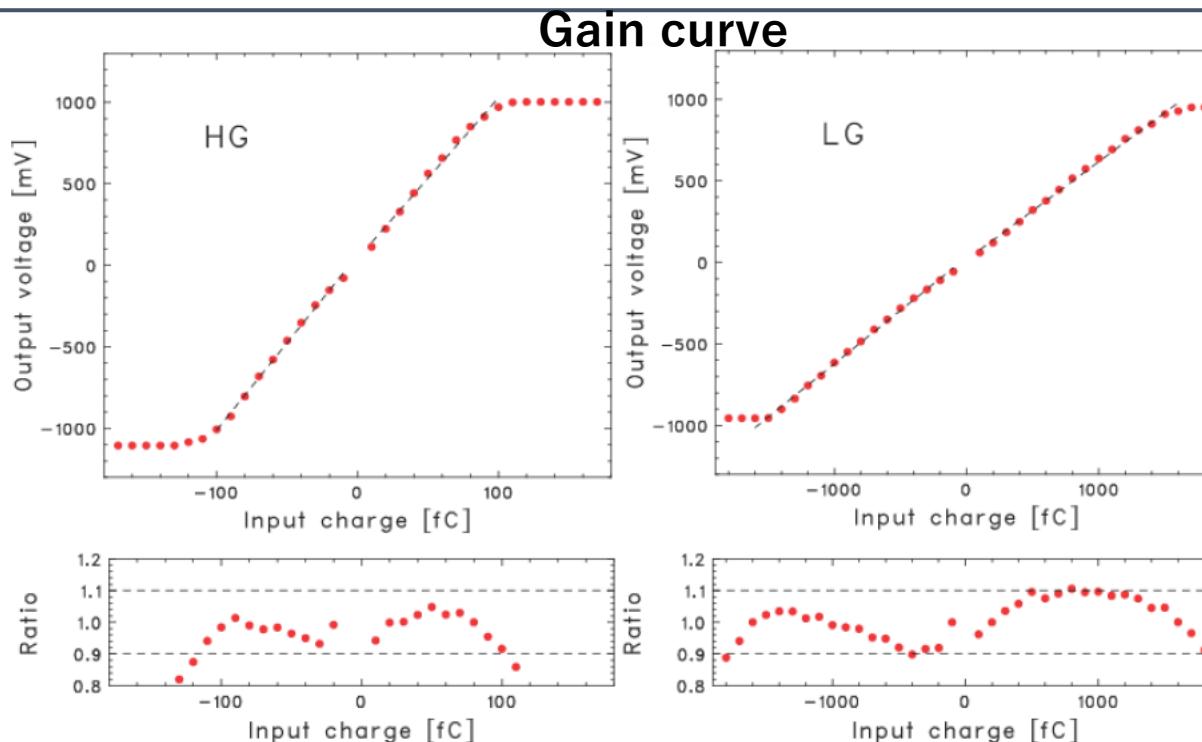

# ゲイン , ダイナミックレンジ

## 要請値

### Gain

HG → 10 mV/fC

LG → 0.5 mV/fC

### Dynamic Range

HG →  $\pm 80$ fC

LG →  $\pm 1600$ fC

\* 直線fit

傾きがGain

\* 測定値とfitの

値の残差

10%以内を

レンジとする

### HG mode

正極性 : 10.0mV/fC 負極性 : 10.7mV/fC

### Gain

### LG mode

正極性 : 0.60mV/fC 負極性 : 0.65mV/fC

| Dynamic Range |         |

|---------------|---------|

| HG mode       | LG mode |

| 100fC         | 1600fC  |

- Gain , Dynamic Range共に両極性で要請値をクリア

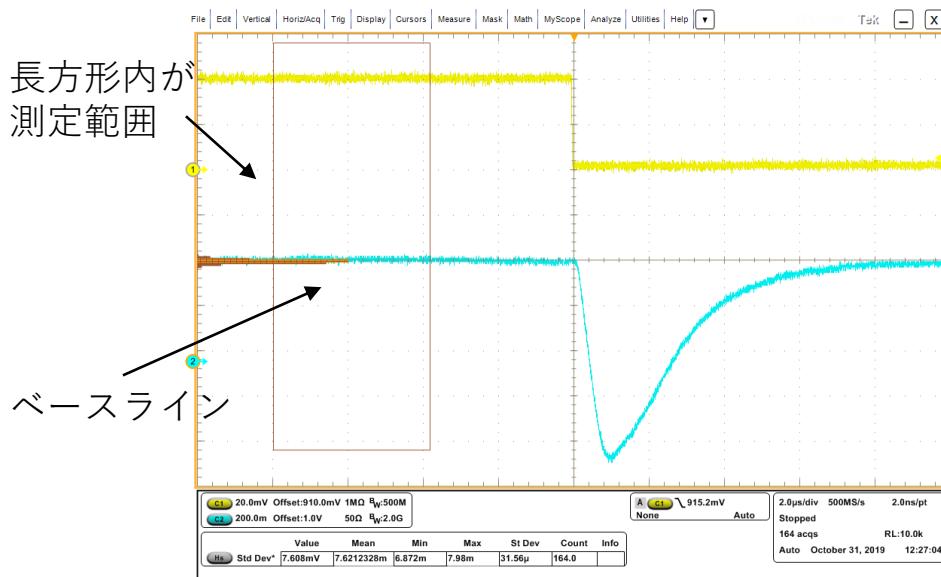

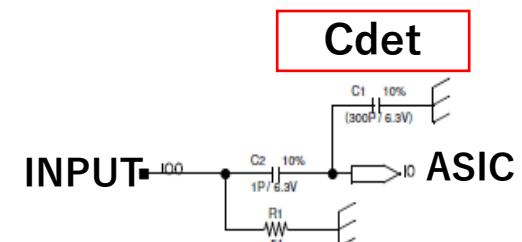

# 検出器容量に対するノイズ特性 評価方法

- ・アナログ信号処理回路からの出力波形をオシロスコープで観測し、ノイズを評価

検出器容量 0pF , 30pF, 120pF, 180pF ,300pF

それぞれに対しての測定を行った。

- ・出力のベースラインのばらつき  $\sigma$  を測定

$$ENC(electron) = \frac{\sigma(mV)}{G_c(mV/fC) \times 1.6 \times 10^{-4}(fC)}$$

$\sigma$  : ノイズ電圧

$G_c$  : コンバージョンゲイン

入力電荷-80 fCにおける出力波形(Cdet=300 pF)

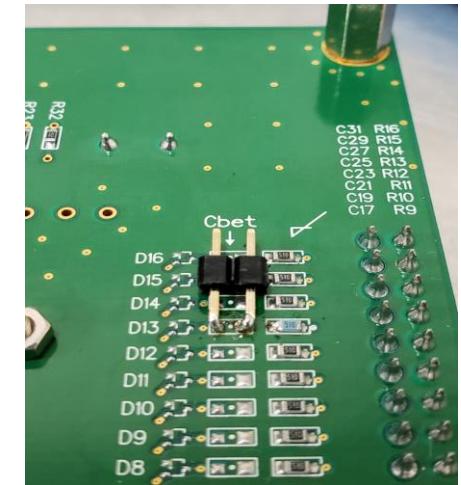

Cdet接続部分

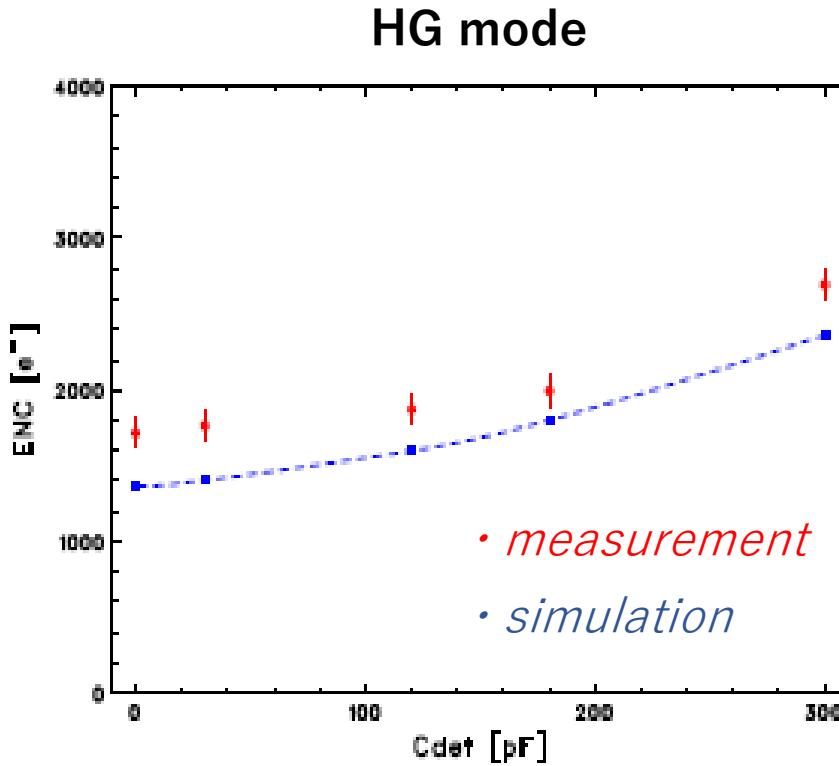

# 検出器容量に対するノイズ特性

要請値

$$\begin{aligned} ENC &= 3000 \text{ } e^- \\ @ C_{\text{det}} &300 \text{ } pF \end{aligned}$$

測定値

$$\begin{aligned} ENC &= 2695 \text{ } e^- \\ @ C_{\text{det}} &300 \text{ } pF \end{aligned}$$

- シミュレーションと比較すると

10%程度のオフセットが乗っている

ASICをPCBにワイヤボンディング

した際の浮遊容量などが原因で

あると考えられる

1 MIP 10fCと仮定しても

**S/N 10以上を確保している**

# ゲイン自動切り替え機能

## ゲイン自動切り替え 仕組み

- CSAの出力電圧の絶対値とコンパレータの閾値電圧絶対値( $V_{th}$ )を比較

- CSA出力電圧絶対値 $< V_{th} \rightarrow$ High gain

- CSA出力電圧絶対値 $> V_{th} \rightarrow$ Low gain

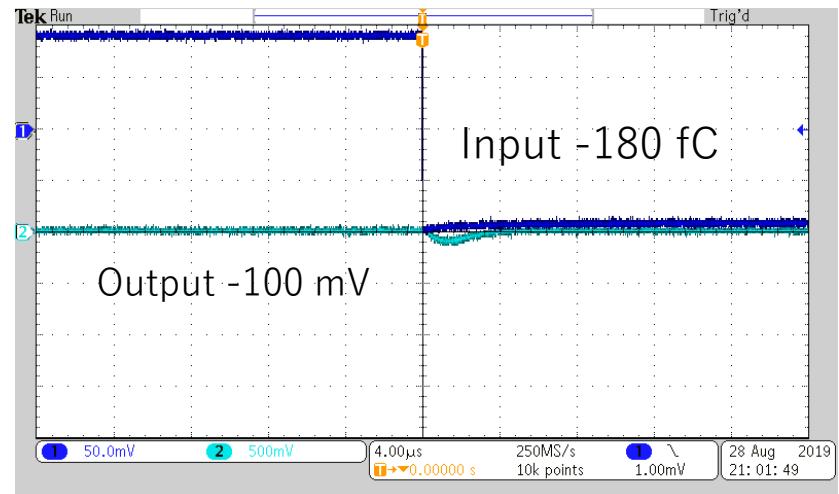

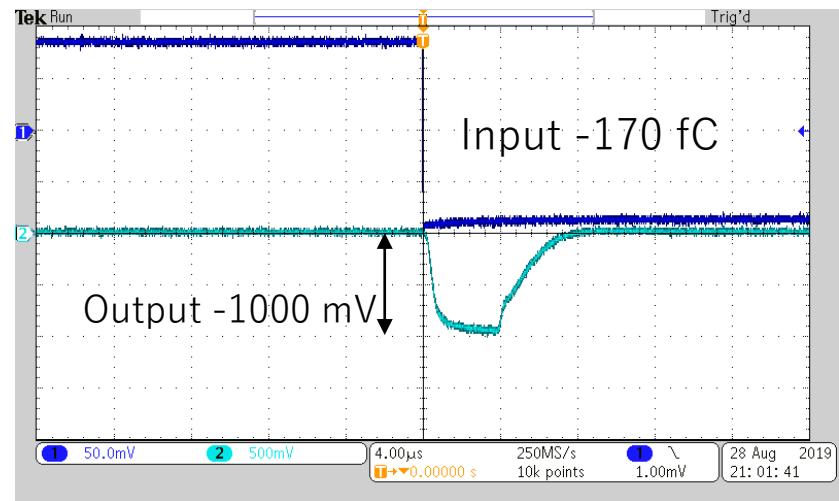

今回の測定では-10fCから測定を開始、-10fCずつ入力電荷量を大きくして-170fC (HG mode)から-180fC (LG mode)になるとゲインが切り替わる様子を確認

ゲインが自動で切り替わる様子

# 低温試験セットアップ

- ・ LArで満たされた容器にSIRONEKOボードを挿入

- ・ FPGAボードとSIRONEKOボードは分離し、測定を行っている

- ・ SIRONEKOボードの出力部を容器外のオシロスコープに接続し、データ取得

\* FPGAボードは

-185°Cでの動作保証がないため

低温容器外に配置

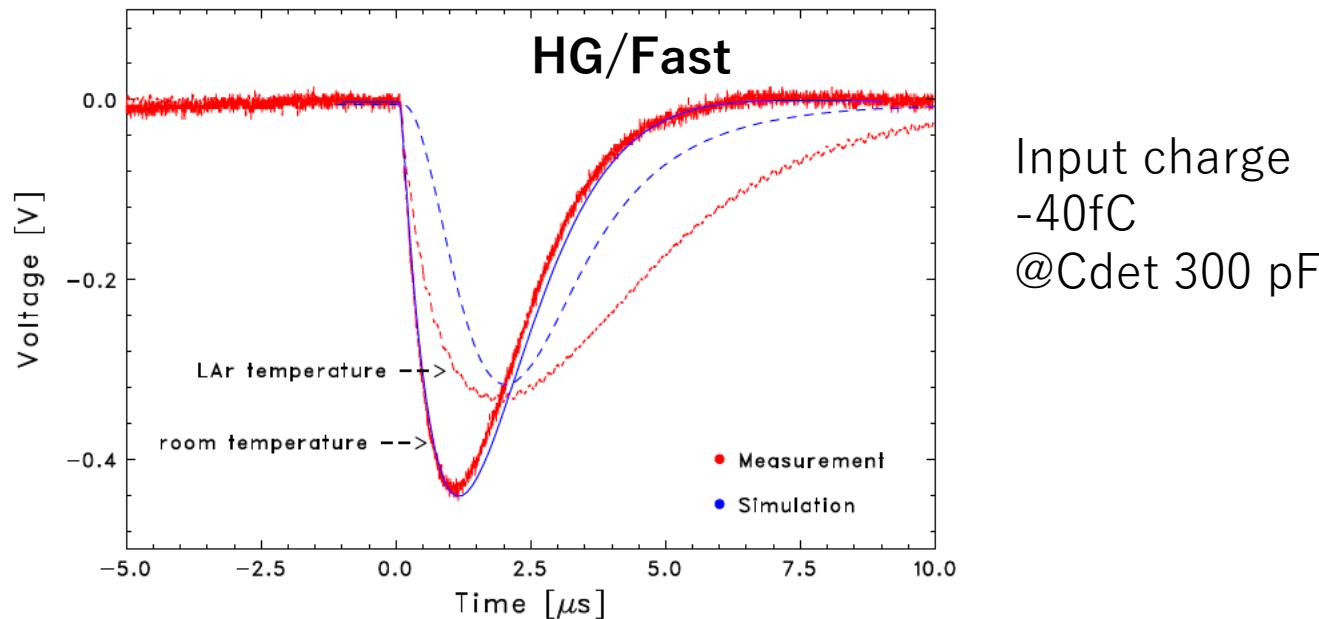

# 極低温試験 アナログ出力波形

## 低温環境での測定結果

- Gain 6.6 mV/fC

- Peaking Time 1.6  $\mu$ s

- 室温での試験と比較すると

Gainは約**40%**低下、Peaking Timeも**60%**増加

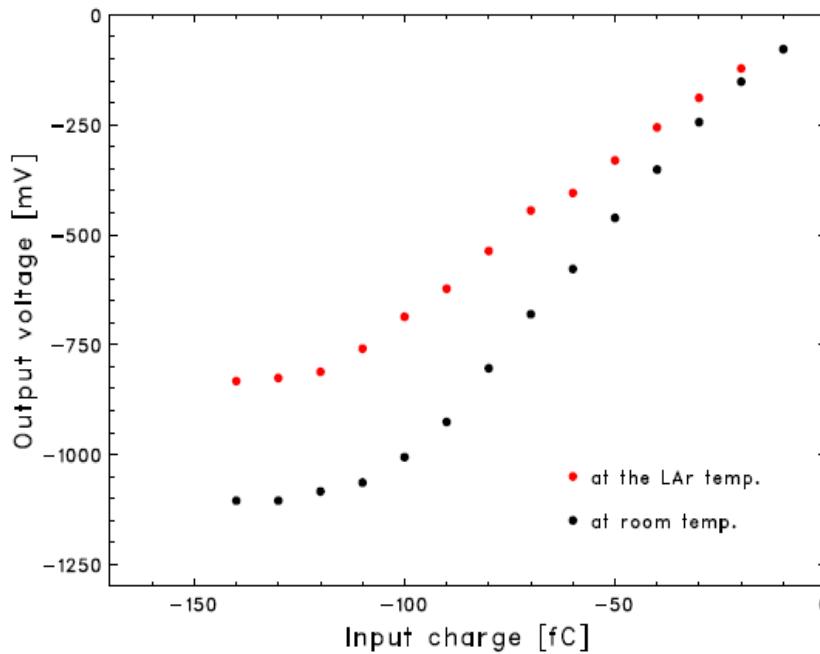

# 極低温試験 ゲインカーブ

HG mode

@Cdet 300 pF

室温試験と低温試験でゲインカーブの比較

- ・ゲインは下がっているが、線形性はOK

温度が下がることでトランジスタの閾値がシフトし、

デバイスの動作点が変化

それによって回路に想定通りのバイアス電流が供給できていなかった

# ファームウェアの開発

今、SIRONEKO + GoSHIK

検出器実装のため準備を進めている

ASICからのADCデータを

FPGAで処理してデータ取得を行

うファームウェアの開発

- 最大10MHz sampling

4000sample/ch 分のデータ取得

- NIM規格の信号をトリガーとして使用

- Ethernetを通じてPCとFPGA間の通信

- Gibabit Ethernet通信使用可能

- ASICのパラメータ変更

# ファームウェアの開発

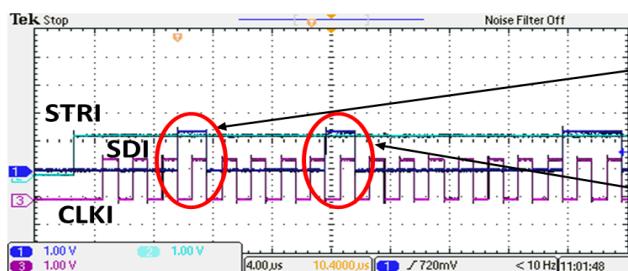

## ASICのスローコントロールに関して

### 使い方

- x2A & x2Bに値を書き込む

(どの機能を使うか)

- x2Cにchの指定

(どのchに適用するか)

- x2Dで出力の開始

| MSEL | SET30 | SET12 | SET06 | LVDS | SLOW | DIFF | POS | ADIN |

|------|-------|-------|-------|------|------|------|-----|------|

| H    | L     | L     | L     | L    | H    | L    | L   | L    |

MSB

アナログ出力とSlowで出力を確認したい場合

global

Ch毎

| SDIで制御するパラメータ | 役割                              |

|---------------|---------------------------------|

| ADIN_ENB      | ADC入力のスイッチング                    |

| POS           | コンパレータの極性(H→+、L→-)              |

| DIFF_ENB      | ADCへの入力の切替(シングルエンドor差動)         |

| SLOW_ON       | Fast/Slowの切替                    |

| LVDS_ENB      | LVDS出力の切替(H→0/1.8 V、L→±300 mV)  |

| SET06         | LVDSの出力信号の振幅の設定(3 bit)          |

| SET12         |                                 |

| SET30         |                                 |

| MSEL          | MONY_FINISH、CMP_ADCの出力信号のスイッチング |

| VTH           | コンパレータの閾値電圧(6 bit)              |

| VTH           |                                 |

| TEST          | テストパルス入力ラインのON/OFF              |

| SEL_MON0      | コンパレータへ送るCSAの出力のON/OFF          |

| SEL_MON1      | Shaper出力のON/OFF                 |

MSEL (1) 0x2Aに1を書き込む

SLOW (8) 0x2Bに8を書き込む (書き込む値は16進数)

Chを0に指定して、0x2dにアクセス

CLKIの立ち上がりで

SDIを読む

ちょうど4クロック目

同様に9クロック目

時定数変更

# ファームウェアの開発

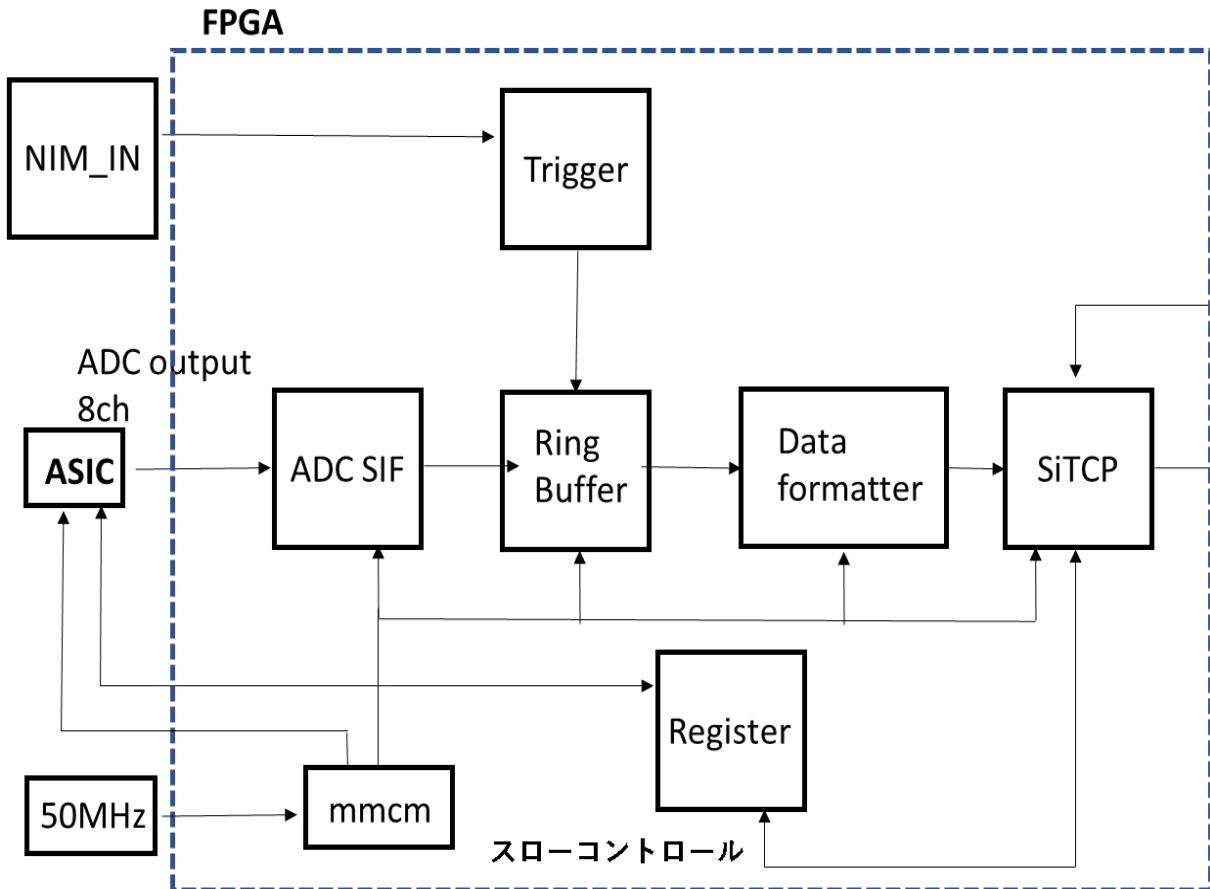

ファームウェアブロック図

- GoSHIKに搭載されている50MHzのクロックから

FPGA内のモジュールに必要なクロック(160MHz, 125MHz)の生成

- ASICのデジタル部動作に必要なクロック(sysclk, sample, load)も

FPGA側で生成し、送信

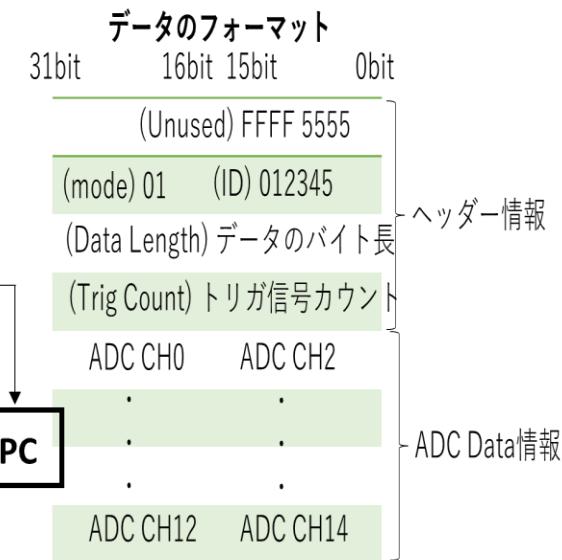

```

00000000 ff ff 55 55 01 01 23 45 00 00 fa 00 00 00 00 00

00000010 00 3f 00 3f 00 7f 00 3f 00 7f 00 01 1f 00 7f

00000020 00 3f 00 3f 00 7f 00 7f 00 7f 00 01 1f 00 7f

00000030 00 3f 00 3f 00 7f 00 3f 00 7f 00 01 1f 00 7f

00000040 00 3f 00 3f 00 7f 00 7f 00 7f 00 01 1f 00 7f

00000050 00 3f 00 3f 00 ff 00 3f 00 7f 01 1f 00 7f

00000060 00 00 00 00 00 00 00 00 00 00 00 00 7f 00 00 7f

```

出力フォーマットの確認

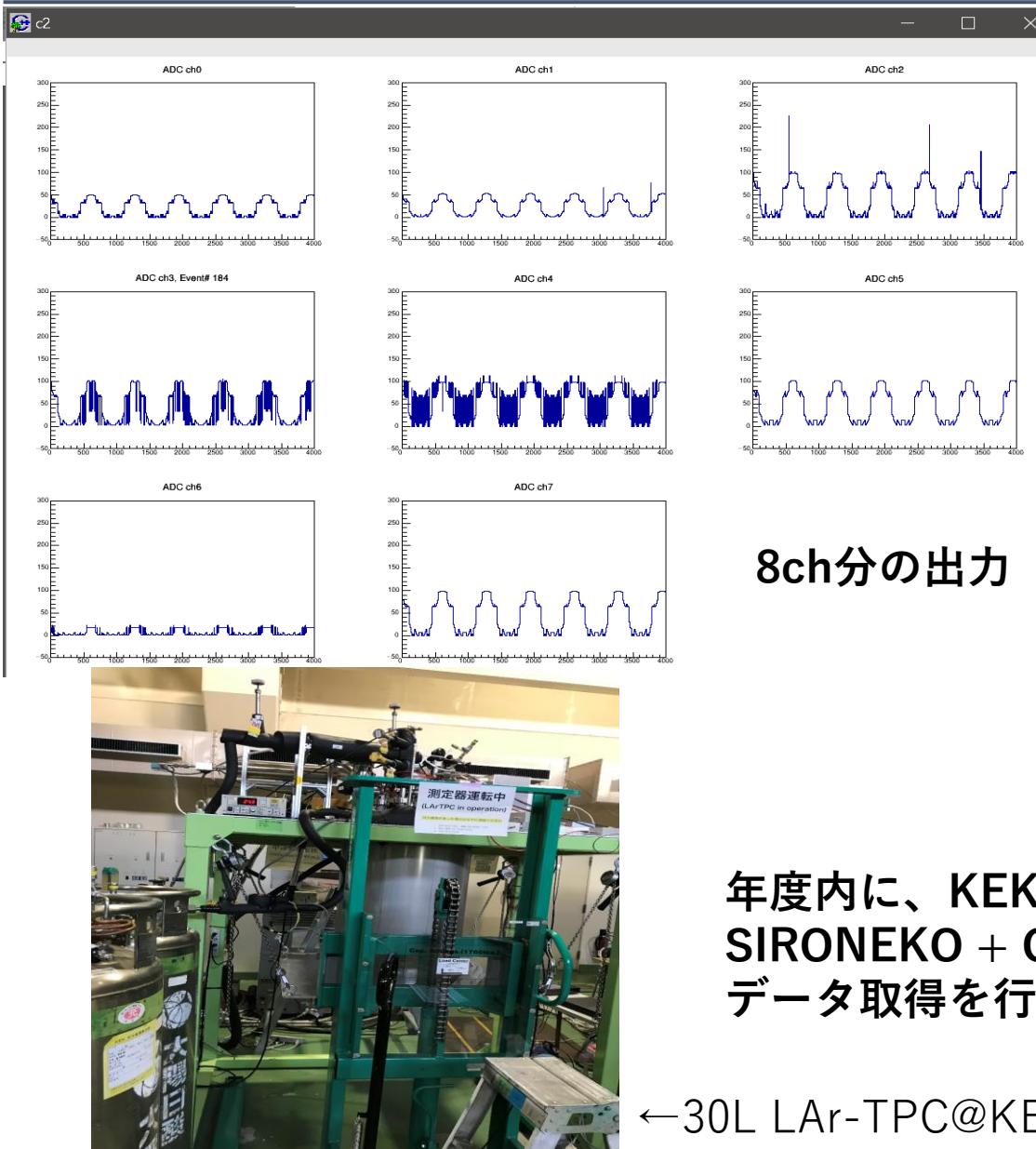

# ファームウェアの開発

ASICのADCにTest Pulse

を入力することが出来るので

Sin波を入力

8ch分の出力

今後

- データとクロックのタイミング調整などをして、波形が正しく見えるように開発する

年度内に、KEKの30L LAr-TPCに

SIRONEKO + GoSHIKを実装して

データ取得を行いたい

# まとめ

LAr-TPC, NI $\mu$ TPCで汎用的に用いる信号読み出しエレクトロニクス

LTARS2018\_K06Bの開発

## 基礎特性試験(室温)、低温試験の結果

- ・ 室温での基礎特性試験

→ **Peaking Time , Conversion Gain , Dynamic Range**に関して

要請値を達成することができている。

**ENC**に関しても要請値を達成し、 **S/N10 以上**で読み出す事が可能である

室温でのアナログ性能は運用可能なレベル

- ・ 低温環境下では、アナログ波形を取得した結果、

Gainが減少し、 Peaking Timeが増加する様子が確認出来た。

→ 室温と同バイアス条件で回路を動作させることが出来ないことを確認

## ファームウェア開発

- ・ Test PulseをADCに入力して出力の確認

## 今後の課題、予定

- ・ ファームウェアに関して、クロックのタイミングが合っていない、

入力に対して出力が正しく出力されていない

- ・ 年度内にKEKの30L LAr-TPCにSIRONEKO + GoSHIKで

検出器に実装、宇宙線試験を行う