### FPGA Firmware Progress Log

Aman Sahoo under supervision of Prof. Mikihiko NAKAO

as of July 23, 2025

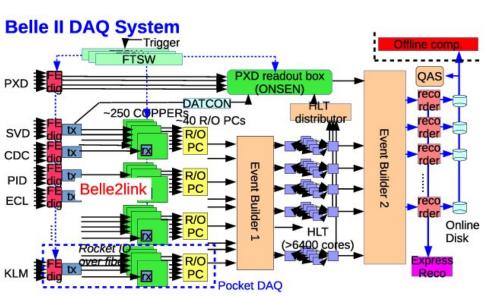

### Belle II Subdetectors

#### 7 Major Subdetectors:

- PXD Pixel Detector: Vertex detection close to interaction point

- SVD Silicon Vertex Detector: Precise tracking of charged particles

- CDC Central Drift Chamber: Momentum measurement and tracking

- TOP Time-of-Propagation Counter: Particle identification (barrel region)

- ARICH Aerogel Ring-Imaging Cherenkov: Particle ID (forward endcap)

- ECL Electromagnetic Calorimeter: Measures energy of photons/electrons

- KLM  $K_L^0$  and Muon Detector: Muon detection and  $K_L$  meson ID

### Trigger and Timing System Overview

### Level-1 Trigger (L1):

- Hardware-based trigger system

- Reduces event rate to 30 kHz

#### **Need for Synchronization:**

- Event-level correlation across subsystems

- Accurate distribution of trigger + time info

#### Trigger Timing Distribution (TDD):

- System-wide clock to FEE, COPPER, trigger

- Run number, trigger type, event number, timestamp to FEE

- Injection veto and revolution signal broadcast

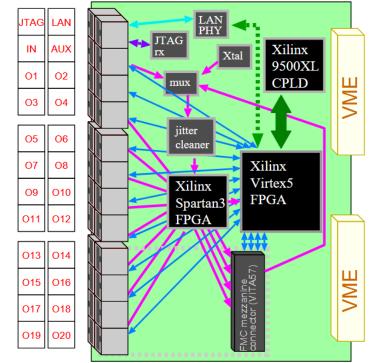

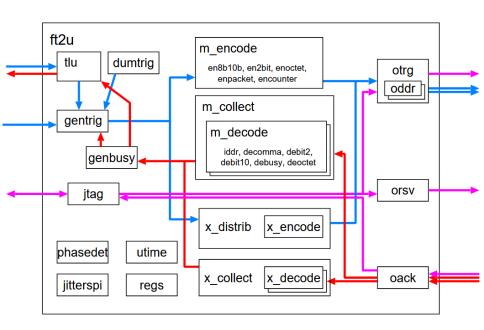

### Clocking and FTSW Boards

#### **Clock Synchronization:**

- SuperKEKB RF clock at 508.9 MHz

- ullet Divided by 4 ightarrow 127.16 MHz (used by FTSW)

#### FTSW - Frontend Timing Switch:

- FPGA-based boards

- Aggregate FEE data + trigger + timing

- Transmit using b2tt protocol

# 01-led (08/07/2025)

- No pattern executed; all LEDs were on simultaneously (static).

- Edit (10/07/2025): Code did not function correctly. Likely cause

was declaring one\_sec in the sensitivity list of the process without

invoking its check within the process body.

```

proc_second: process (clk_l) — changes value of one_sec

every second

begin

if rising_edge (clk_l) then

-some code

one_sec <= not one_sec:

end if:

end process:

proc_seq: process (one_sec)

```

## 02-cycle-led (10/07/2025)

- Pattern cycling functionality achieved.

- Arrays were defined and used as Look-Up Tables (LUTs).

- LUTs contained explicitly described patterns and number of cycles per pattern.

- **Downside:** Every pattern and cycle count was manually typed instead of being generated via logical derivation.

- **Next Step:** Streamline the code and explore more sophisticated architectural design.

# 03-led-cycle-proc (10/07/2025)

- Produced nearly identical output as 02 by dividing functionality into two processes:

- One for counting seconds.

- One for tracking cycles and outputting LED signals.

- Gained understanding of proper use of rising edge and synchronization principles.

- Plan to split main process into further subsystems to assess modularity benefits.

- Curiosity: Each cycle lasts twice as long as specified. Temporarily resolved by halving time, but root cause needs investigation.

```

proc_second: process (clk_l) - changes value of one_sec every second

begin

if rising_edge (clk_l) then

if cnt_lclk = ONE_SEC_31MHZ - 1 then

cnt_lclk \le (others \Rightarrow '0');

else

cnt_lclk \le cnt_lclk + 1;

end if:

end if:

end process;

proc_seq: process (clk_l)

begin

if rising_edge (clk_l) and cnt_lclk = 0 then

— lots of nested if-else statements to handle sequence changes

- FTSW3 LED is active—low ('0' for ON / '1' for OFF)

o1ledg_o \le not sea_led(0):

o3ledg_o \le not seq_led(1);

o5ledg_o \le not seq_led(2);

o7ledg_o \le not seq_led(3);

interval \le interval - 1:

end if:

```

# 04-fast-pattern (15/07/2025)

- Developed simple VHDL code to generate signals faster than previous 1-second LED patterns.

- Signals generated every clock cycle (effectively every 4 clock cycles at 127 MHz).

- Utilized oscilloscope for signal visualization.

- Only TRG channel was used for output.

- Pattern: x cycles up, x cycles down, where  $x \in \{1, 2, 3, 4\}$  and changes every second.

- Learned to use circuit schematics and .NET files to generate .UCF files.

- Improved understanding of:

- Differential signals

- IOBUFDS

- Signal manipulation

- Next Step: Utilize RSV and ACK channels and design more complex

```

map_o_trg: obufds port map ( i=> trg_out, o => o_trg_p, ob => o_trg_n );

proc_second: process(clk_l)

begin

- code to keep count of runtime in seconds

end process proc_second;

proc_pattern: process(clk_l)

begin

if rising_edge(clk_l) then

if cnt | clk = 0 then

clock\_cvcle\_up \le clock\_cvcle\_up + 1:

elsif clock_cycle_up = "00" then

trg_out <= signal_base(0);

elsif clock_cvcle_up = "01" then

trg_out <= signal_base(1);

elsif clock_cycle_up = "10" then

trg_out <= signal_base(2);

elsif clock_cycle_up = "11" then

trg_out <= signal_base(3);

else

trg_out <= '0': — default case

end if:

Update signal_base for next cycle

```

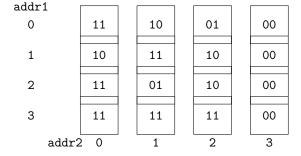

# 05-fast-pattern-lut (16/07/2025)

- Extended to include RSV channel alongside TRG for output signal pairs.

- Patterns stored in LUT, updated every second.

- Each pattern starts with a unique "00" signal to indicate sequence start.

- Improved modularity:

- LUT coded in a separate file: pattern\_lut.vhd

- Instantiated in top module via work library.

- Yet to use FOR loops due to wrap-around behavior of std\_logic\_vector.

- Next Step: Test signal functionality on FTSW-3 board.

```

- diff sig output - through obufds

map_o_trg: obufds port map ( i=> trg_out

, o \Rightarrow o_{trg_p}, ob \Rightarrow o_{trg_n});

map_o_rsv: obufds port map ( i =>

rsv_out. o \Rightarrow o_rsv_p. ob \Rightarrow

o_rsv_n ):

- lookup table for pattern generation

map_lut: entity work.pattern_lut

port map (

addr1 \Rightarrow row,

addr2 \Rightarrow col.

result => pattern ):

— processes

proc_second: process(clk_l)

begin

— code to keep time

end process proc_second;

proc_pattern: process(clk_l)

begin

if rising_edge(clk_l) then

trg_out <= pattern(0);

```

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE STD LOGIC UNSIGNED ALL:

use IEEE.NUMERIC_STD.ALL:

entity pattern_lut is

port (

addr1 : in std_logic_vector(1

downto 0); — 2-bit address

input

addr2 : in std_logic_vector(1

downto 0);

result : out std_logic_vector(1

downto 0) ):

end pattern_lut:

architecture rtl of pattern_lut is

type lut_type is array (0 to 3, 0 to

3) of std_logic_vector(1

downto 0):

constant lut : lut_type := (

"11", "10", "01", "00"),

"10", "11", "10", "00"), "11", "01", "10", "00"),

"11", "11", "11", "00")

begin

```

### LUT-Based Signal Output Diagram

#### Output:

result(1) = Signal 1

result(0) = Signal 2

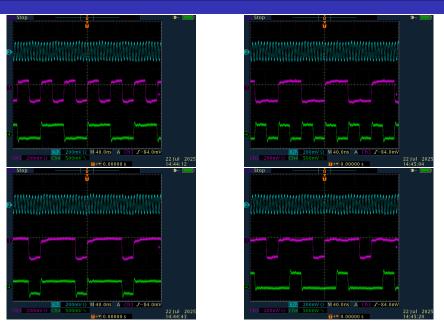

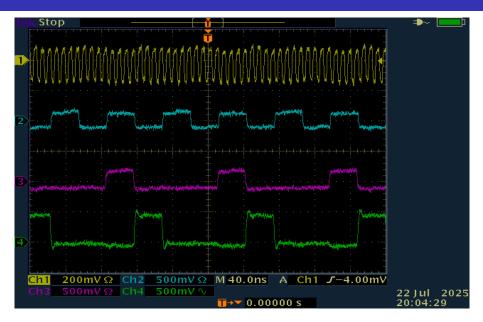

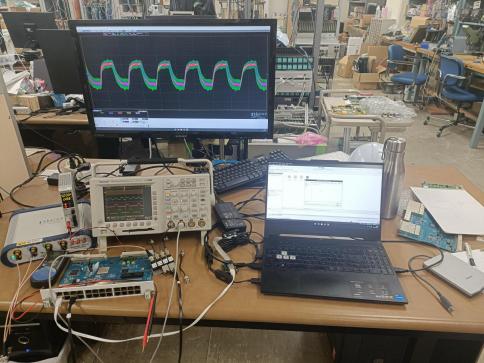

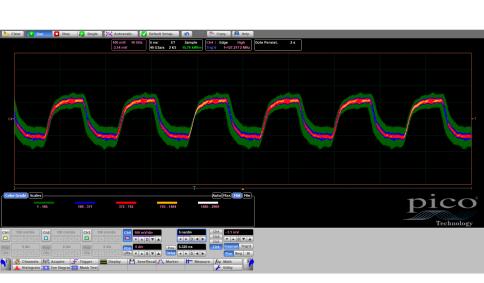

# 06-signal-testing (22/07/2025)

- Based on design from 05-fast-pattern-lut to test all FPGA output/input ports (LAN and AUX excluded).

- All port channels used: CLK, RSV, ACK, TRG.

- Defined three 20-bit vectors to map specific outputs per channel per port.

- Created obufds\_module and instantiated in top module.

- Purpose: Convert std\_logic\_vector signals to differential output vectors.

- Used generate statement to replicate obufds for each port.

- Added LED logic: LED pattern shifts every 0.5 seconds for verification.

- Results:

- Verified output from all ports (OUT-1 to OUT-20) using oscilloscope and LEDs.

- LED, RSV, TRG, ACK channels operate correctly.

- CLK channel functions on odd-numbered ports, but fails on even-numbered ports.

- Requires further investigation.

```

proc_pattern: process(clk_l)

begin

if rising_edge(clk_l) then

trg_out <= ( others => pattern

(0)):

rsv_out <= ( others => pattern

(1));

ack_out <= ( others => pattern

(2)):

col \le col + 1;

end if:

end process proc_pattern;

proc_led: process(clk_l)

begin

if rising_edge(clk_l) then

if cnt_lclk = (ONE_SEC_31MHZ)

/2) - 1 or cnt_lclk =

ONE_SEC_31MHZ - 1 then

led <= not led;</pre>

end if.

o_led_{v_b} \le (others \Rightarrow led);

o_ledg_b <= (others => not led

```

```

entity obufds_module is

port (

trg_out : in std_logic_vector (20

downto 1):

o_trg_n : out std_logic_vector (20

downto 1):

o_trg_p : out std_logic_vector (20

downto 1)

- similar ports for rsv and ack

):

end obufds_module;

architecture rtl of obufds_module is

begin

GEN_OBUFDS: for x in 1 to 20 generate

map_o_trg: obufds port map ( i =>

trg_out(x), o \Rightarrow o_trg_p(x).

ob \Rightarrow o_trg_n(x);

map_o_rsv: obufds port map ( i =>

rsv_out(x), o \Rightarrow o_rsv_p(x).

ob \Rightarrow o_rsv_n(x);

map_o_ack: obufds port map ( i \Rightarrow

ack_out(x), o \Rightarrow o_ack_p(x),

ob \Rightarrow o_ack_n(x));

end generate GEN_OBUFDS;

```

end rtl:

## Cable Equipment

Aman Sahoo under supervision of Prof. Mik

FPGA Firmware Progress Log

## Cable Equipment

# Thank You!

Questions and Discussion Welcome