# MicroTCA-based LLRF systems used at the STF at KEK

MicroTCA WS Japan 2025 2025/08/28

Mathieu Omet

(on behalf of the RF group and the iCASA SRF group)

#### Contents

- LLRF systems at STF-II

- Outlook for LLRF system for the ILC CM prototype

- LLRF system at the STF vertical test stand

- Summary

## LLRF systems at STF-II

#### Introduction

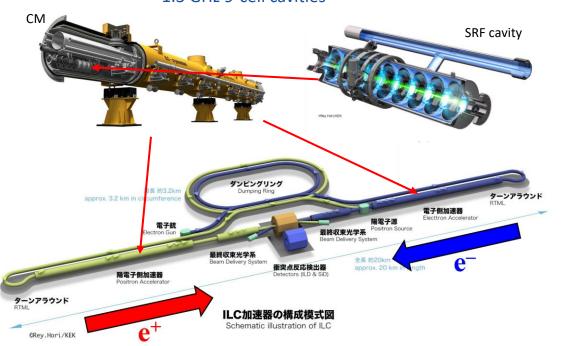

- International Linear Collider (ILC)

- Future Higgs factory machine

- 250 GeV center of mass energy

- Superconducting cavity / cryomodule technology

- Based on TESLA technology

- ~ 8,000 superconducting radio frequency (SRF)

1.3 GHz 9-cell cavities

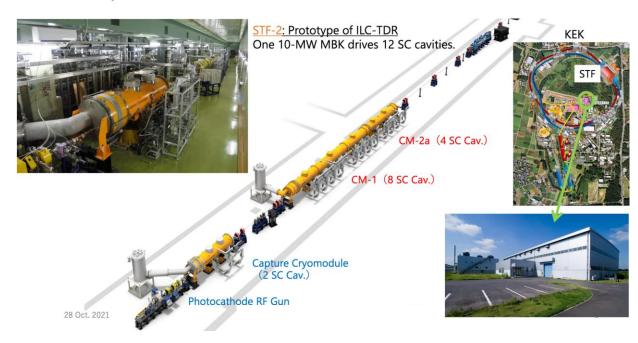

- STF-II Accelerator at KEK

- ILC prototype / R&D accelerator

- 1 normal conducting 1.3 GHz gun cavity

- 2 SRF 9-cell cavities in the capture CM

- 12 SRF 9-cell cavities in 2 main linac cryomodules

- Operated 2015 -

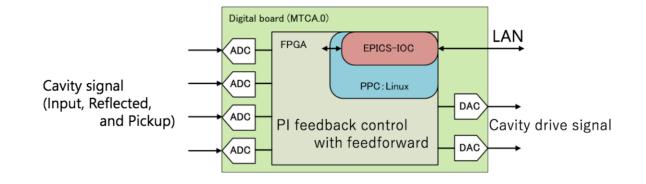

# MicroTCA.0-based board developments for accelerators at KEK

In 2008 the development MTCA.0based LLRF hardware for the usage at SuperKEKB, cERL, and STF was conducted

- Cavity field controller/monitor

- Multiple ADC and DAC channels

- Virtex-5 FX FPGA

- Wind River Linux installed on PPC 400

- EPICS-IOC

- Was used to operate the STF-II gun and the capture CM

- FPGA (Virtex 5 FX),

- 4 x 16-bit ADCs (Max. 130MSPS)

- 4 x 16-bit DACs

- Digital I/O

Mitsubishi Electric TOKKI System Co., Ltd.

- FPGA (Virtex 5 FX),

- 2 x 14-bit ADCs (Max. 400MSPS)

- Digital I/O

Mitsubishi Electric TOKKI System Co., Ltd.

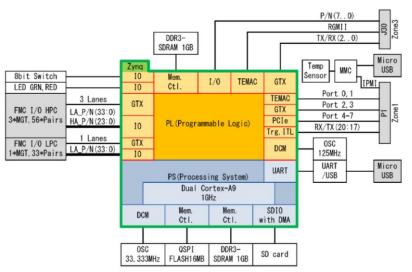

# MicroTCA.4-based board developments for II C

- In 2013 a digital system with ILC LLRF control in mind was started

- Required more than ten 16-bit ADCs and two 16-bit DACs as well as an optical connection

- Resulting product

- Based on MTCA.4

- FPGA and CPU (Zynq-7000 SoC, XC7Z045)

- ARM-linux installed on Cortes-A9

- EPICS-IOC

- FPGA (Spartan 6, XC6SL150T)

- ADC, DAC, vector-sum

Block diagram inside Zynq-7000 of newly developed board

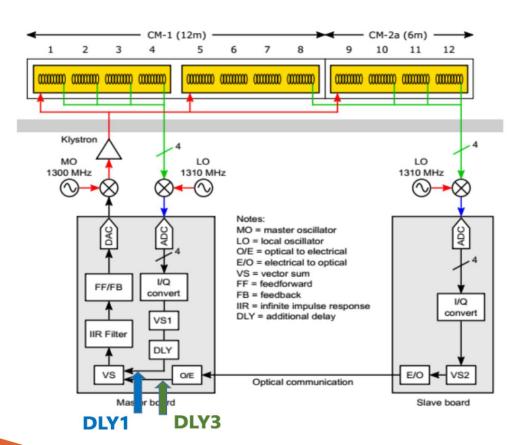

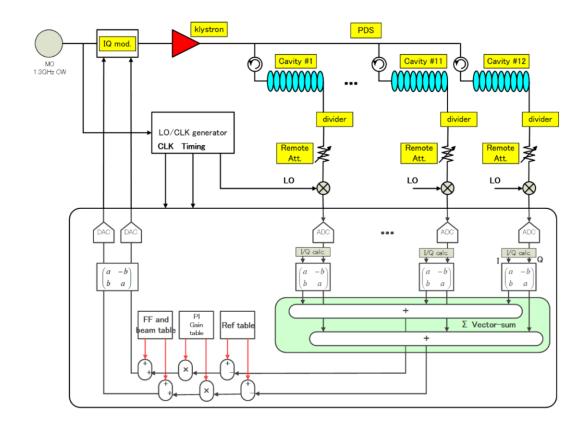

#### Configuration of ILC LLRF system

Figure 3.43. Implementation block diagram for the DKS LLRF system

In the ILC, 39 SC cavities are operated under cavity-field vector-sum feedback control.

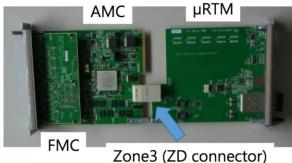

#### Newly developed board based on MTCA.4

Mitsubishi Electric TOKKI System Co., Ltd.

#### \_0..00 (\_\_\_ 0.

O AMC & FMC

2 FPGAs (Zyng-7000 SoC, Spartan 6)

- 14 x 16-bits ADCs

- 2 x 16-bits DACs

$\bigcirc$   $\mu$ RTM

- 2 x SFP

- 1 x RJ-45

- Digital I/O

# Power supply box for MTCA.4 AMC and RTM

#### MTCA.4 crate

- Boards comply with MTCA.4 standard

- Can be operated in MTCA.4 crate

- We developed and are using a custom power supply box

Used to operate STF-II main linac (12 cavities in CM1 and CM2a)

#### **Power supply box**

Front side

Rear side

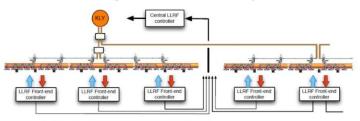

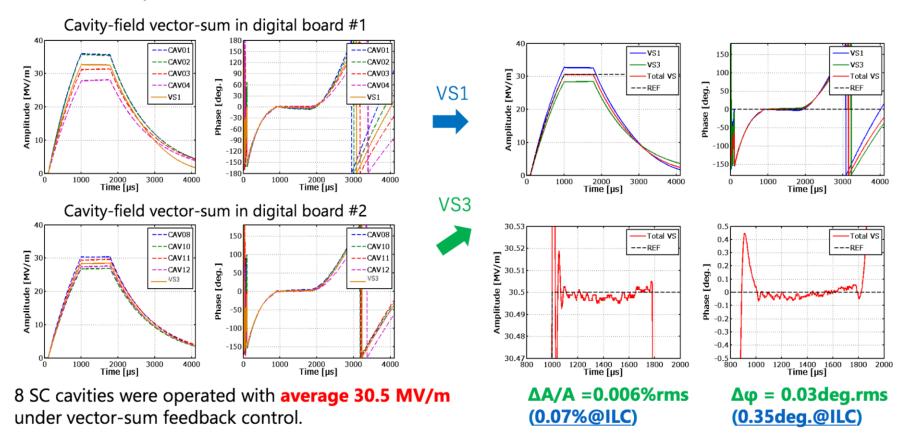

### STF-II main linac LLRF system overview

Two systems were connected via an optical link in a master-slave configuration

On the master board feedforward (FF) and the vector-sum PI feedback (FB) are implemented

#### Achievements of STF-II LLRF system operation

Amplitude and phase stabilities

- Maximum beam energy gained in CM1/2a with 12 cavities: 343.7 MeV

- Maximum average accelerating gradient with 9 cavities: 32.9 MV/m

# Outlook for LLRF system for the ILC CM prototype

### ILC Prototype Cryomodule

- From 2023 to 2027 we are building and testing an ILC prototype cryomodule at KEK

- In scope of MEXT ATD and the ILC Technology Network

- Currently developing all necessary infrastructure

- Plan to develop and implement a MicroTCA.4based LLRF system very similar of the STF-II LLRF system

- New feature: better integration with the cavity frequency tuner piezo driver

- Dedicated keynote talk:

| ILC spec.     | E <sub>acc</sub> | $Q_0$       |

|---------------|------------------|-------------|

| Vertical test | 35 MV/m          | 0.8 x 10E10 |

| Cryomodule    | 31.5 MV/m        | 1.0 x 10E10 |

Keynote Talk: Future Linear Collider and its LLRF system

Shinichiro MICHIZONO

Bldg. #3 Seminar Hall, High Energy Accelerator Research Organization (KEK), Tsukuba Campus

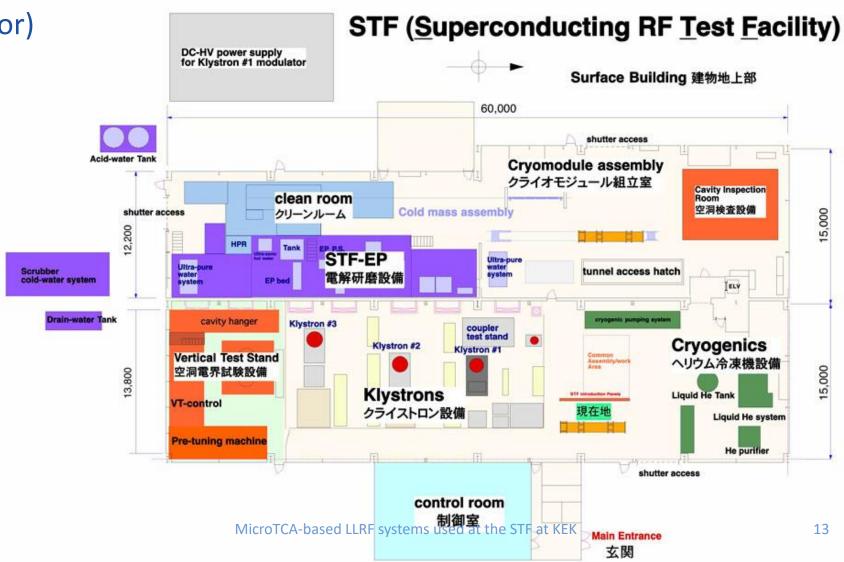

# LLRF system at the STF vertical test stand

#### Introduction

Superconducting RF test Facility (STF)

STF-2 (ILC R&D accelerator)

- SRF facilities

- Inspection

- Pre-tuning

- Electro polishing

- Clean room

- Vertical test stand

### STF vertical test stand for SRF cavity R&D

Control

Helium dewars

Cryo pits 1 & 2

VTpreparationarea

Power amplifier

### Current RF system for STF VT stand

- >20 years old

- All analog

- Important channels are monitored in EPICS

- No automation

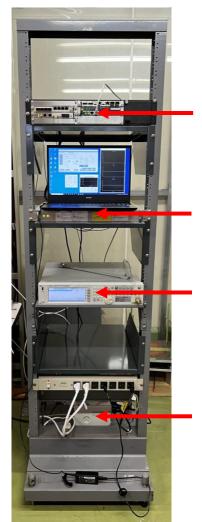

# Component overview of new MTCA.4-based LLRF system

- Decided to buy "of-the-shelf system"

→ MTCA.4

- Collaboration with DESY

- Component list

- RackPak/M5-1, 2HE 6-Slot MTCA.4 Crate

- NAT-MCH-PHYS80

- AM G64/471-41, AMC CPU with Xeon E3-1505M, 16GB RAM and onboard 256GB SDD

- NAT-PM-AC600D (Single Full-Size AC PSU)

- NAMC-psTimer

- SIS8300-KU MTCA.4 Digitizer FPIO 8AC2DC DZ3 125 MS/s 16-bit 10 Kanal 4 x 4 Gbit

- DWC8VM1 R13 1.3 GHz RF FP 11 MTCA.4 Downconverter/Vektor Modulator RTM

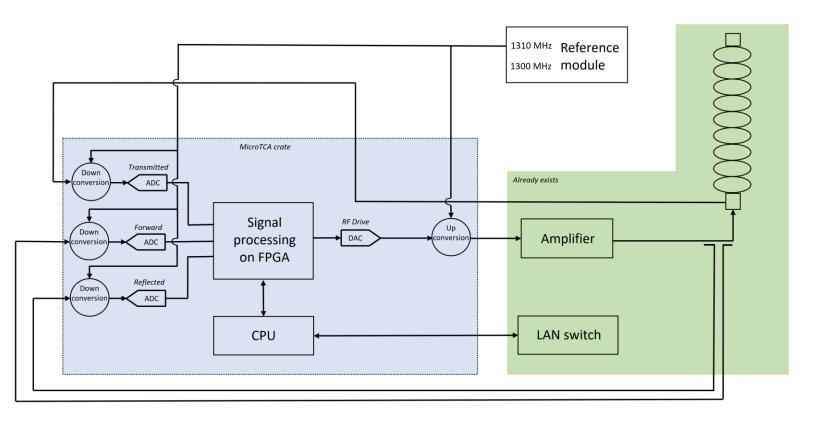

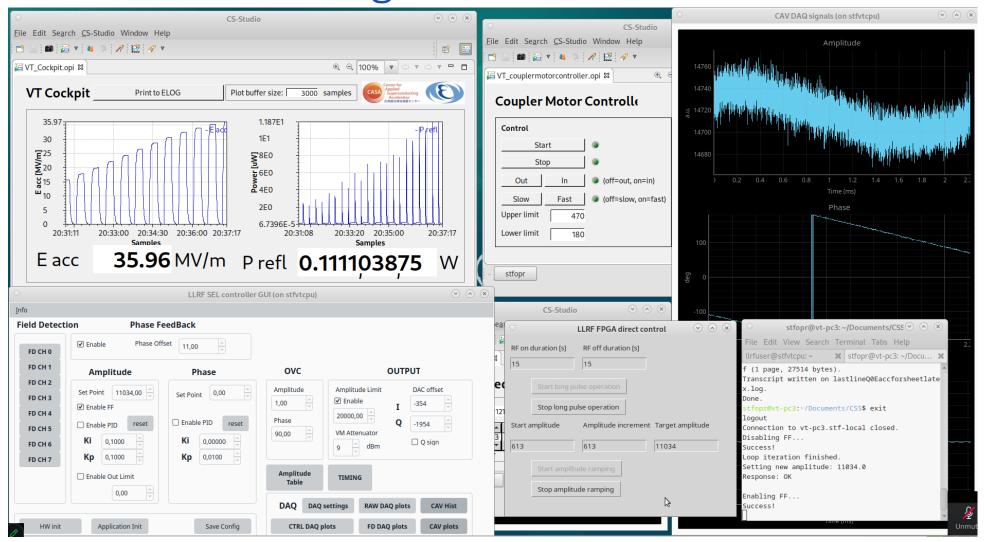

#### LLRF system at STF VT area

MicroTCA.4 crate

UniLOGM

Signal generator

Power converter

## Schematic of LLRF system

#### Schematic of the LLRF system for the KEK STF VT stand

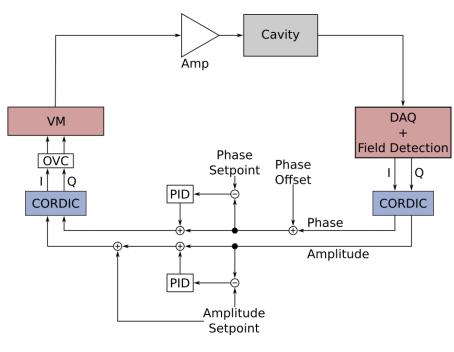

#### Schematic of the SEL controller

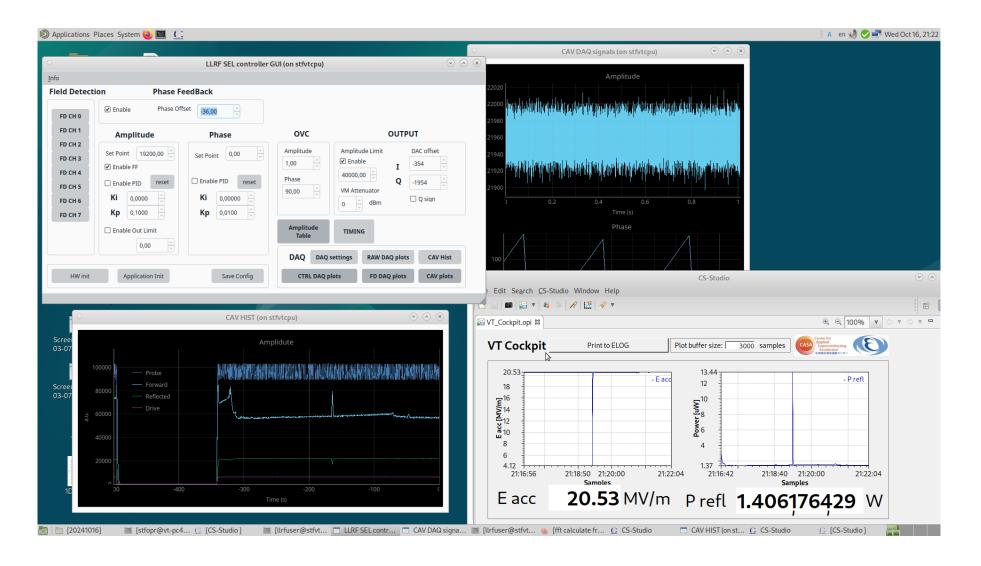

## SEL CW drive of single-cell cavity

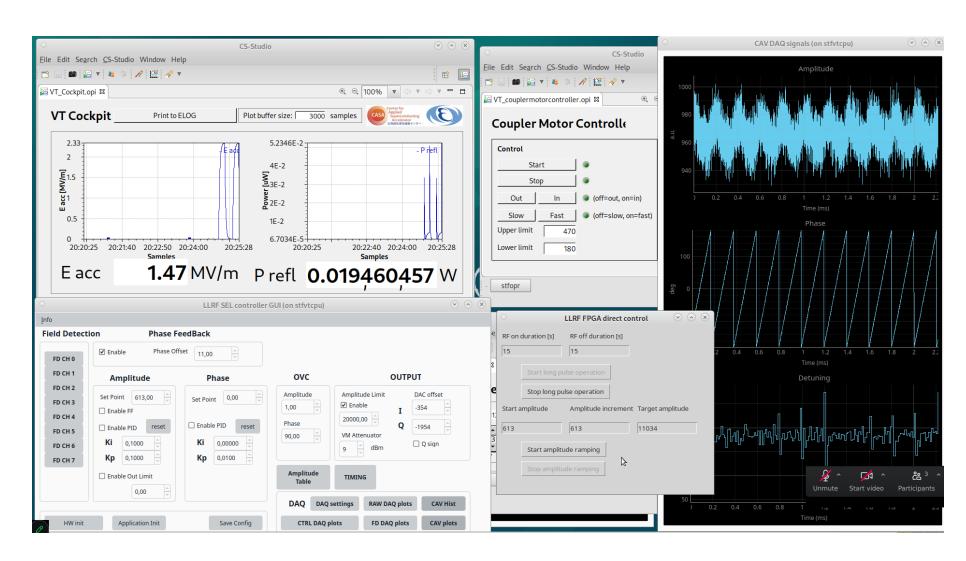

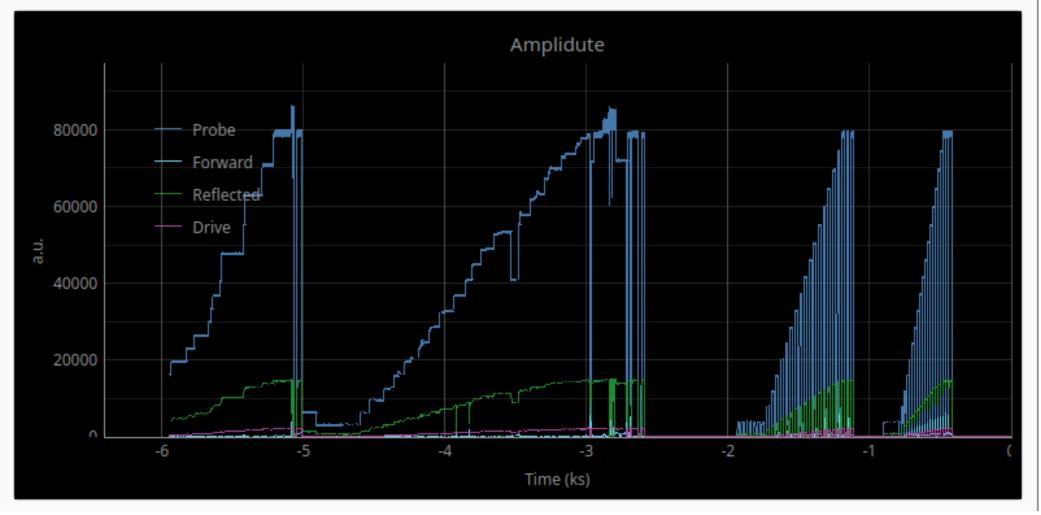

## Test of long pulse operation

- Certain 9-cell cavities to be tested in scope of the ILC prototype CM production might need long pulse operation

- High-level software script was implemented, which allows arbitrary pulse lengths

### Automated long-pulse ramp-up and automated data taking

#### Comparison of ramp-up procedures

Manual ramp-up (30 mins.)

Automated long-pulse ramp-up (10 mins.)

Automated CW ramp-up (5 mins.)

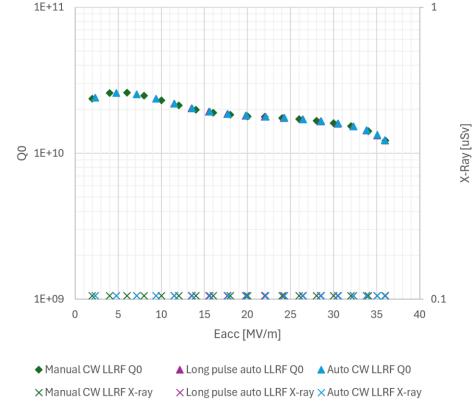

# Automated CW ramp-up and automated data taking

- Identical curve as manually ramped up

- Identical to long pulse automatic ramping

Further automation R&D will be presented in this talk:

Automated Passband Mode Resonance Peak Finding Algorithm Using MicroTCA.4-Based Digital LLRF System

Eric Viklund

## Summary

#### Summary

- MTCA.0 and MTCA.4-based LLRF systems were developed at KEK

- Together with Mitsubishi Electri TOKKI System Co., Ltd.

- Successful operation at the SRF-II accelerator

- For the test of the currently being built ILC prototype CM a MTCA.4-based LLRF system will be developed

- A MTCA.4-based LLRF system is currently being commissioned at the STF VT stand

- Goal is a highly automated VT procedure

- Collaboration with DESY

This work was supported by the MEXT Development of key element technologies to improve the performance of future accelerators Program, Japan Grant Number JPMXP1423812204