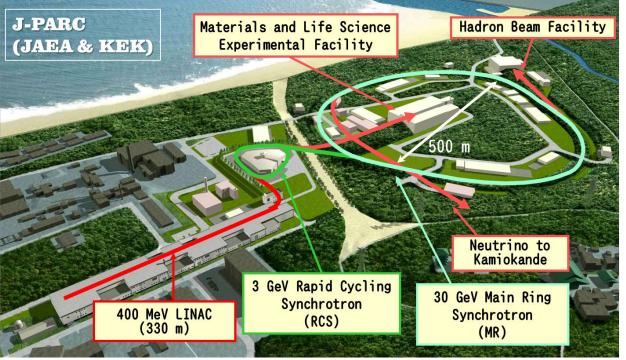

## J-PARC & J-PARC LINAC

J-PARC (Japan Proton Accelerator Research Complex)

### J-PARC Linac

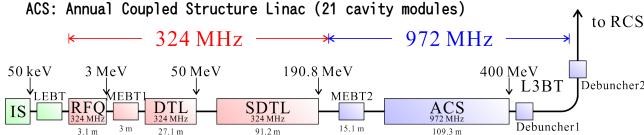

Particles: H<sup>-</sup> (negative hydrogen)

• Kinetic Energy: 400 MeV

Peak Current: 50 mA

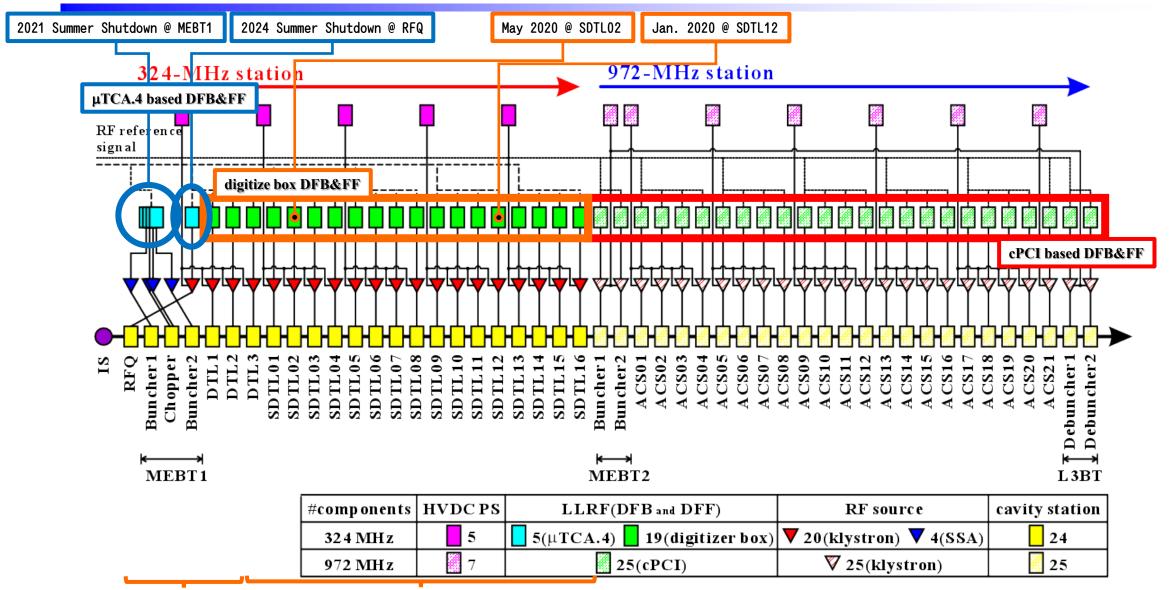

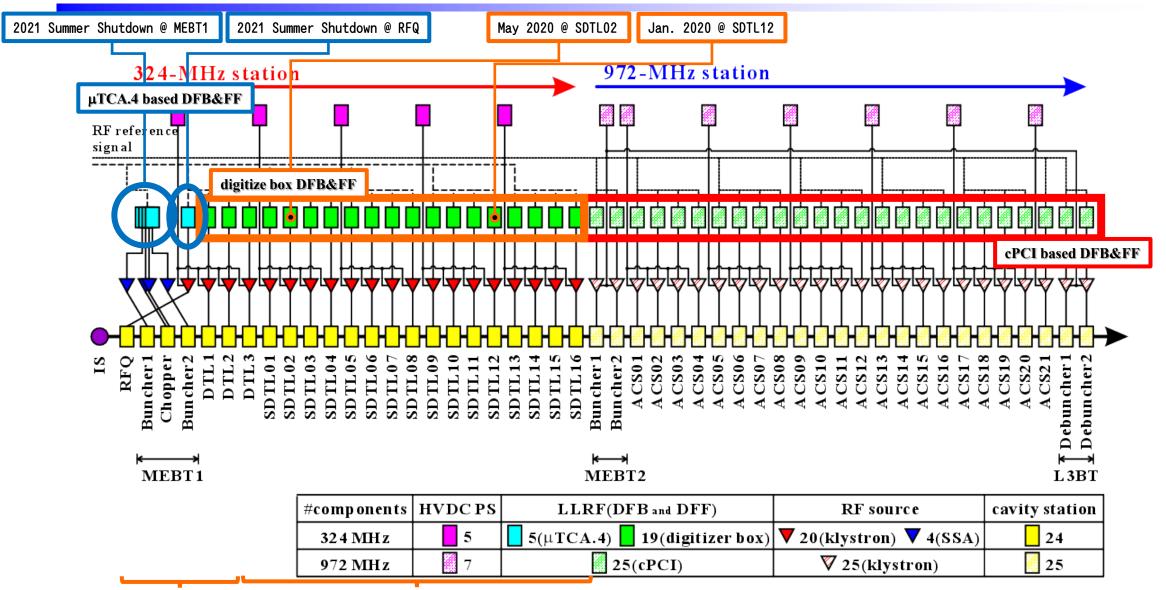

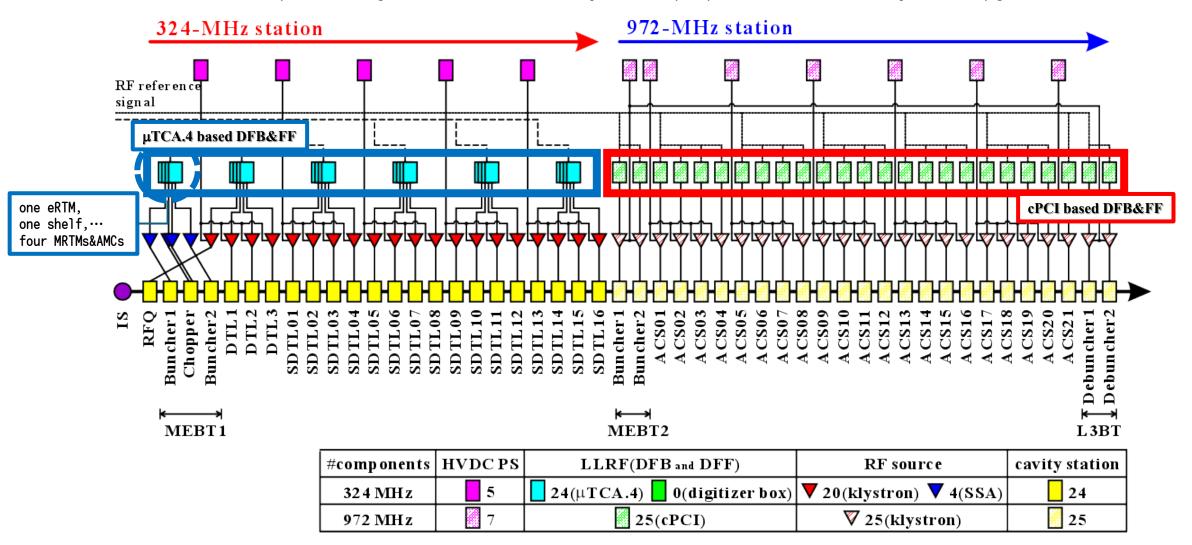

Acceleration Frequency: 324 MHz (24) + 972 MHz (25)

Pulse Width: 500  $\mu$ s (Beam), 650  $\mu$ s (RF)

• Repetition: 25Hz

IS: H<sup>-</sup> Ion Source

RFQ: Radio Frequency Quadrupole Linac DTL: Drift Tube Linac (3 cavity modules)

SDTL: Separate-type Drift Tube Linac (16 cavity modules)

~330 m

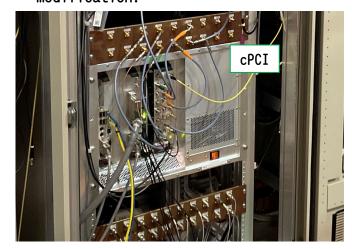

Digital Feedback & Feedfoward (DFB&FF) system based on cPCI

Development: <del>∼early 2000s</del>1999∼.

Start of J-PARC Linac operation: Oct. 2006

Start of J-PARC user operation: Dec. 2008

Required Gradient Stability : ±1% in amplitude, ±1 deg. in phase

- $\rightarrow$  OFB :  $\pm 0.3\%$  in amplitude,  $\pm 0.3$  deg. in phase

- $\rightarrow$  Beam Loading Compensation System :  $\pm 0.3\%$  in amplitude,  $\pm 0.3$  deg. in phase

- → Reference Distribution System : ±0.3 deg. in phase

## DFB&FF System @J-PARC LINAC

### **Previous System:**

cPCI boards for DFB/DFF

✓ FPGA board: discontinued

✓ DSP board: discontinued

✓ CPU board: discontinued

✓ RF&CLK board: discontinued

### development environment

✓ FPGA: Xilinx ISE Ver 6.2i

✓ DSP: TI Code Composer Studio Ver 2.1

✓ host program: Redhat 8.0 gcc compiler Ver 3.2

✓ application: python 2.4/wxPython 2.6

→ We cannot keep the development environment.

→ We gave up on updating the FPGA logic modification.

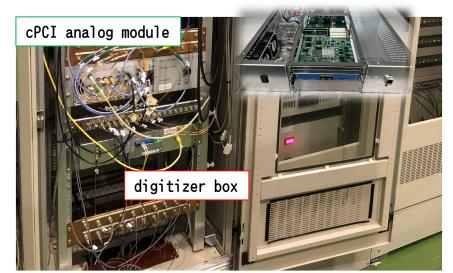

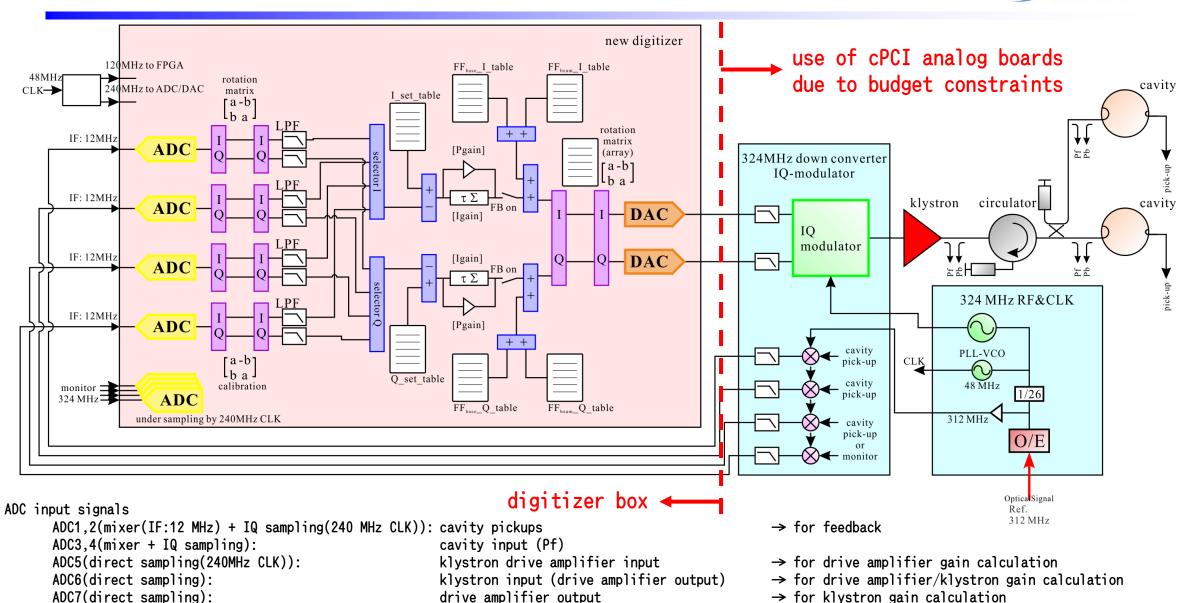

### digitizer box (MEDS):

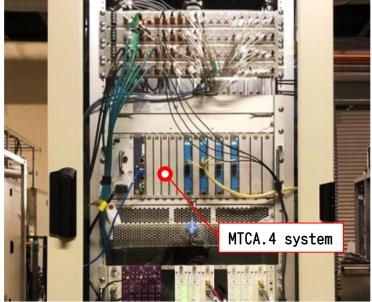

A/D-D/A signal processing MTCA.4 based AMC board

✓ platform: MTCA.4 AMC

✓ FPGA: Zynq XC7Z045-1FFG900C, QSPI FLASH-ROM 16MB, SD-card Remote Update

✓ RAM: DDR3-SDRAM 1GB×2 (PL, PS)

✓ OS: Xilinx Linux (EPICS-IOC)

✓ ADC: 8ch 16bit 370MSPS(max.), BW: 800MHz

✓ DAC: 2ch 16bit 500MSPS

✓ SFP: 2ports

### MTCA.4 based RTM board:

✓ clock generation (120 MHz, 240 MHz)

✓ level conversion

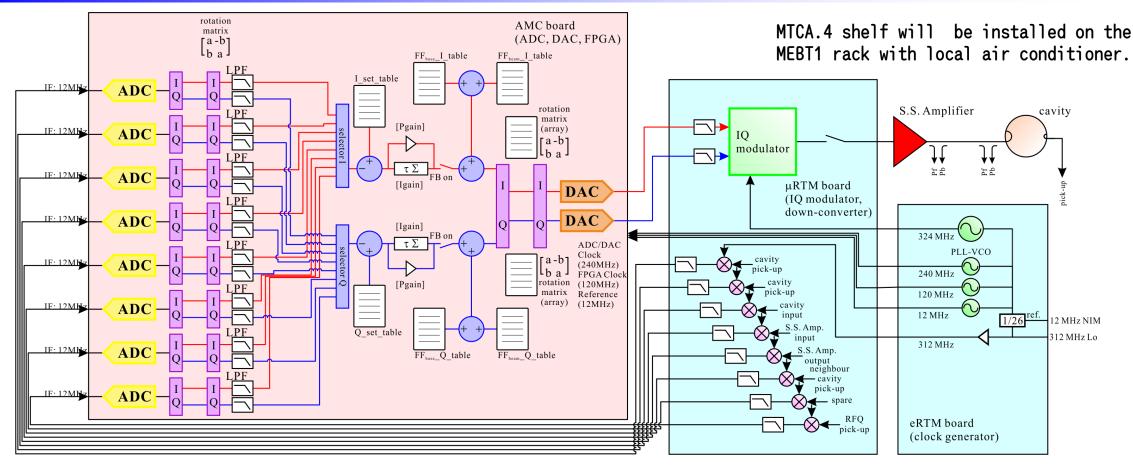

### MTCA.4 w RF backplane (MEDS):

AMC: A/D-D/A signal processing

→ same as the digitizer box

MRTM: 8-ch down-converter, IQ modulator

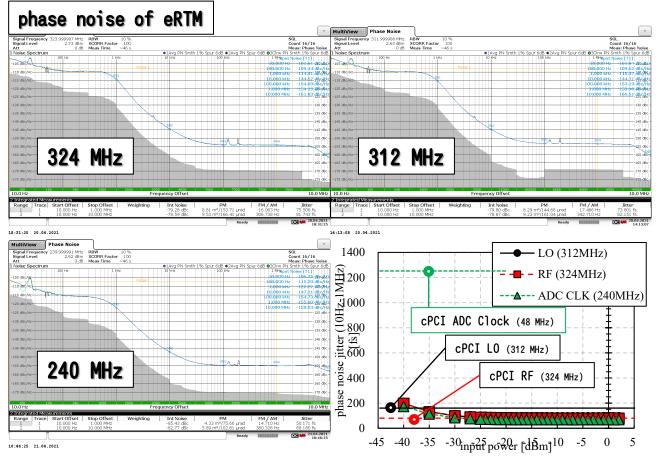

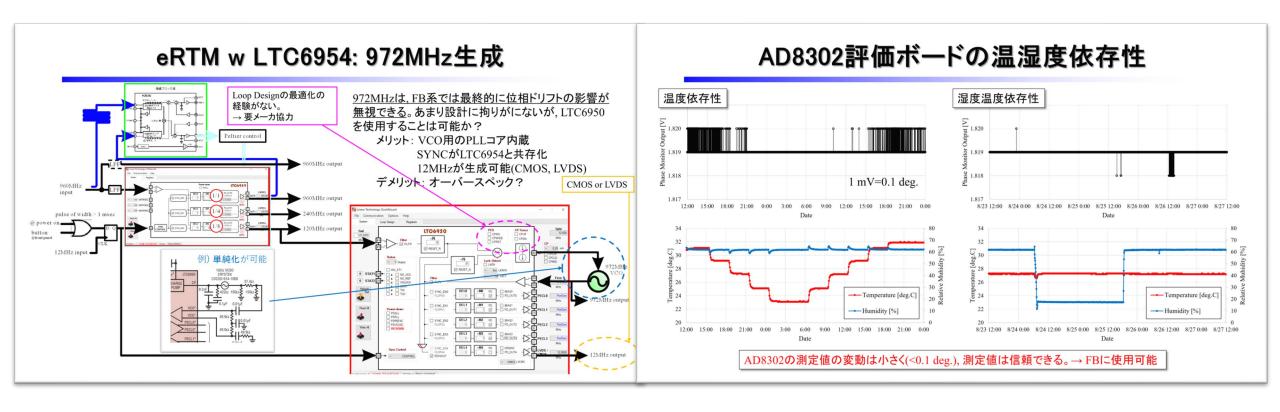

eRTM: clock generator (312 MHz, 324 MHz, 120 MHz, 240 MHz, 12 MHz), distribution

→ manufactured by CANDOX

no communication between boards

# Cavity & RF Status @J-PARC LINAC KEK

# DFB&FF System Using Digitizer Box

neighbor cavity pickup (ex. upstream cavity) → for phase drift check

ADC8(direct sampling):

# DFB&FF System Using MTCA.4 Shelf KEK

ex) ADC input signals, Buncher1 @MEBT1

ADC1,2(mixer(IF:12 MHz) + IQ sampling(240 MHz CLK)): cavity pickups ADC3(mixer + IQ sampling): cavity input (Pf)

ADC4(mixer + IQ sampling): ADC5(mixer + IQ sampling):

ADC6(mixer + IQ sampling): ADC7(mixer + IQ sampling):

ADC8(mixer + IQ sampling):

SSA input SSA output cavity input coupler (Pb) Buncher2 pickup

RFQ pickup

→ for feedback

→ for SSA gain calculation

→ for SSA gain calculation

→ for phase drift check/compensation

→ for phase drift check/compensation

# Performance of MRTM, eRTM Boards KEK

Performance of eRTM, MRTM for J-PARC LINAC LLRF

- ✓ phase noise of eRTM

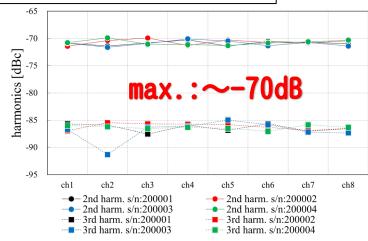

- √ harmonics of IF outputs of MRTM

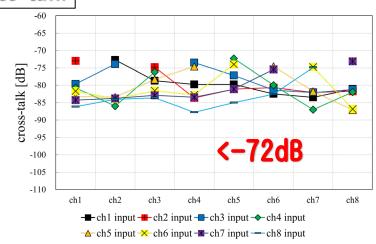

- ✓ cross-talk of MRTM

RF/LO phase noise: almost same as that cPCI RF&CLK board ADC Clock phase noise: greatly improved

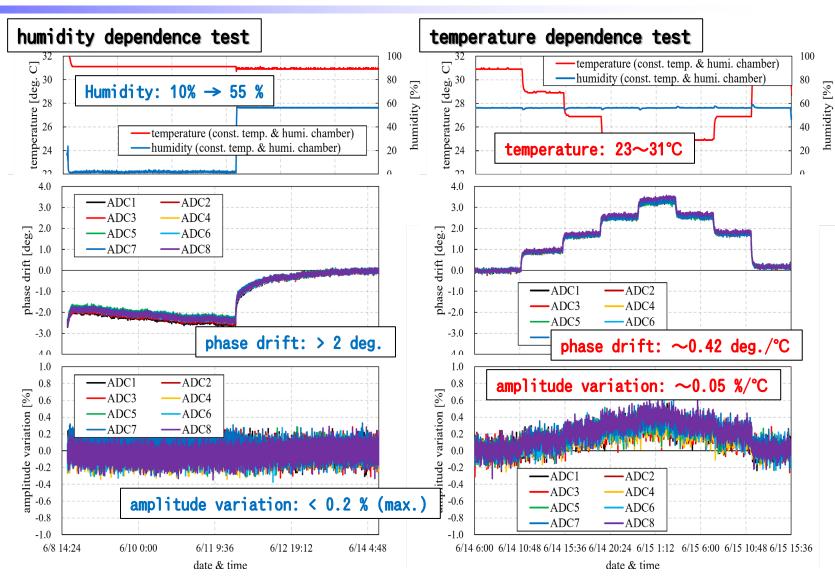

### harmonics of IF outputs of MRTM

-70dB∼0.031%: Neglective on our system

### cross-talk

-72dB∼0.025%: Neglective on our system

# Stability of Amplitude and Phase KEK

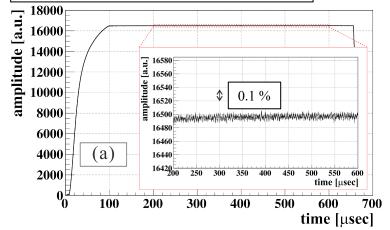

performance  $\sim +/-0.1\%$  in amplitude.  $\sim$ +/-0.1 deg. in phase

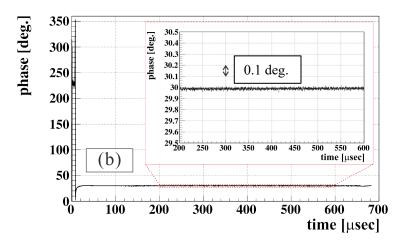

The substrate material (Ro4003C) was tested and sorted in advance, but good results were not obtained as a humidity characteristic test.

# Beam Loading Compensation System KFK

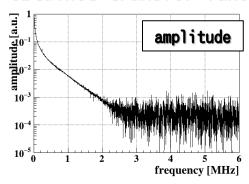

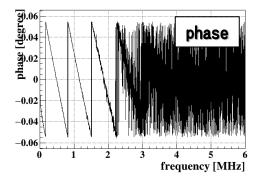

### Obtained transfer function at SDTL01

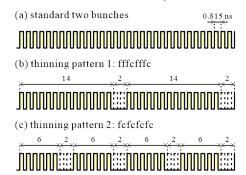

### intermediate pulse

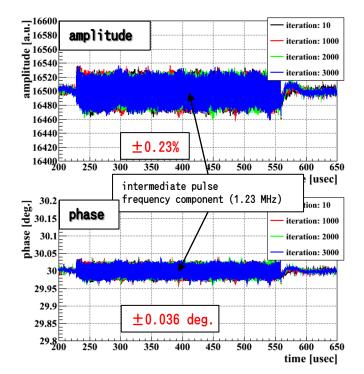

### beam loading compensation

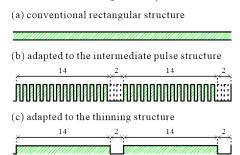

### for standard two bunches @SDTL02

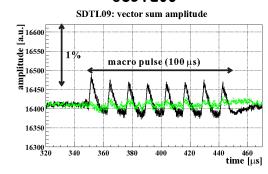

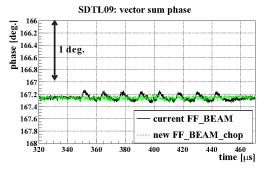

## adapted to intermediate pulse @SDTL09

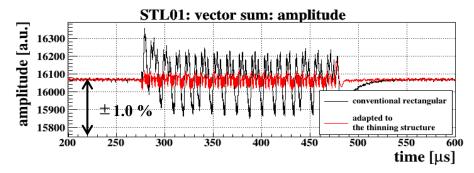

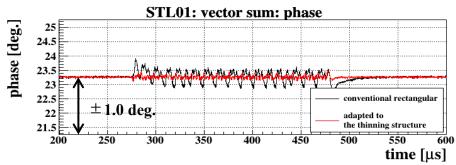

### adapted to thinning structure @SDTL01

# Cavity & RF Status @2025

# Cavity & RF Status @2026

We are purchasing items this fiscal year in preparation for next year's upgrade.

## Logic Test @972 MHz

We "temporarily" installed a digitizer box in the ACS21 station and conducted logic tests.

Results of Beam Loading Compensation

- ✓ wo Beam

- parameter adjustment program (IQ offset, ADC/DAC rotation)

- transfer function measurement

- ✓ w Beam

- Beam loading compensation system

#### for standard two bunchers adapted to intermediate pulse adapted to thinning structure ACS21: vector sum (beam: no-thin): amplitude ACS21: vector sum (beam: fffcfffc): amplitude ACS21: vector sum (beam: fffcfffc): amplitude i 16800 16700 17200 17000 16700 16800 amplitude 16600 16600 16400 16400 16400 16200 no FF\_BEAM adapted to 15800 FF\_BEAM adjustment 320 time [µs] time [µs] time [µs] ACS21: vector sum (beam: no-thin): phase ACS21: vector sum (beam: fffcfffc): phase ACS21: vector sum (beam: fffcfffc): phase phase [deg.] phase [deg.] phase [deg.] 44 1.0 deg no FF BEAM $\downarrow 1.0 \deg$ 44 1.0 deg. adapted to ndapted to FF\_BEAM adjustment the intermediate pulse structure time [µs] time [µs] time [µs]

Excluding detailed adjustments, we confirmed that the logic worked without any issues.

## Hardware Development @972 MHz

The eRTM and MRTM boards for the 972 MHz system are currently under development. The prototypes have already been manufactured, and performance test is in progress.

Feature of 972-MHz DFB&FF prototype system:

The eRTM prototype board implements a phase drift compensation function using the phase detector AD8302. Both the AD8302 and the frequency divider LTC6954/LTC6950 have been tested using evaluation boards.

## Summary

- ✓ We have been developed and operated the cPCI-based DFB&FF system. It is currently being replaced by the MTCA.4-based system, which provides improved performance.

- ☐ Present Status:

- MTCA.4: MEBT1(buncher x2, chopper x2), RFQ

- digitizer box: DTL(3), SDTL(16)

- cPCI: 972-MHz(25)

- □ 2025 (plan):

- MTCA.4: 324 MHz(24=6 sets)

- cPCI: 972 MHz(25)

- ✓ We are confident that updating the digital system of the 972-MHz stations will significantly improve the beam quality.

- ✓ Preparations for the 972 MHz DFB&FF system are also in progress, and replacement to the new system will be implemented sequentially, if the budget allows.