Development of 3D-SOI pixel sensor for the vertex detector of future e<sup>+</sup>e<sup>-</sup> collider

Yunpeng Lu, yplu@ihep.ac.cn

Institute of High Energy Physics, Beijing, China

SOIPIX Quantum Imaging Workshop

Kanazawa, December 1-2, 2025

### **Outline**

- Introduction

- Challenges in vertex detector for future e<sup>+</sup>e<sup>-</sup> experiment

- Features of CPV-4 design and 3D-SOI process

- Sensing diode

- Analog/Digital separation

- 3D compatibility

- Verification of lower tier

- Reverse bias voltage

- Verification of upper tier

- Removal of handle wafer

- Verification of 3D integration

- connectivity

- Summary and Outlook

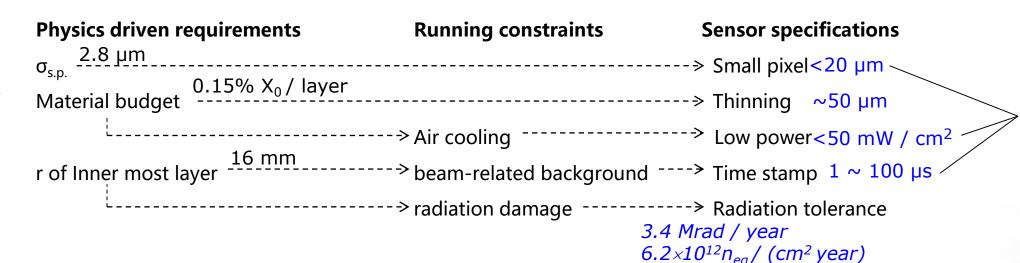

### Requirements of Vertex detector for the future e+eexperiment

Measure charged particles with <u>high position resolution</u> at <u>high collision rate</u>

Impact parameter resolution

$$\sigma_{r\phi} = 5 \oplus \frac{10}{p(GeV)\sin^{3/2}\theta} (\mu m)$$

Vertex sub-detector is the inner-most part of collider experiments

Challenges in pixel design

Reference detector

for CEPC

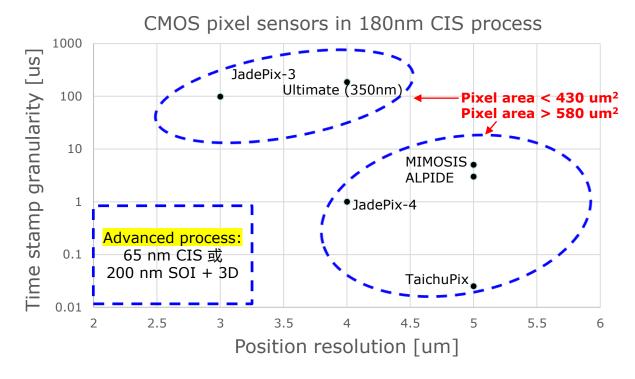

# Trade off between Position resolution and Time stamp granularity

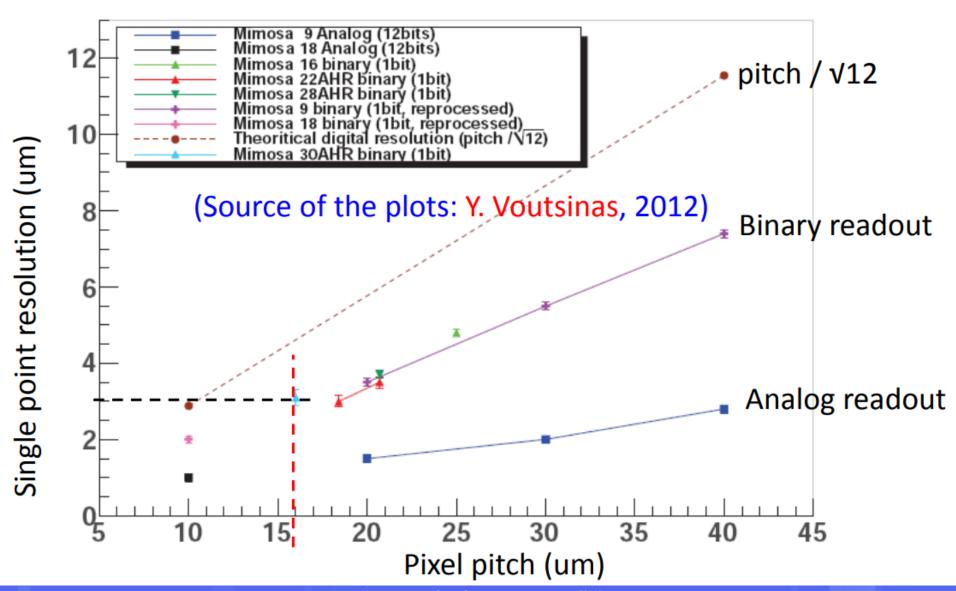

- Comparison of pixel sensors using <u>180nm CIS process</u>

- Small pixels lose time resolution

- Fast time stamp use more pixel area

| Name      | Pixel size<br>[um²] | Position<br>Resol. [um] | Time Stamp<br>[us] | Readout<br>scheme  | Pixel area |

|-----------|---------------------|-------------------------|--------------------|--------------------|------------|

| MIMOSIS   | 26.88x30.24         | 5                       | 5                  | Data driving       | 812        |

| ALPIDE    | 28x28               | 5                       | 3                  | Data driving       | 784        |

| TaichuPix | 25x25               | 5                       | 0.025              | Data driving       | 625        |

| JadePix4  | 20X29               | 4                       | 1                  | Data driving       | 580        |

| Ultimate  | 20.7x20.7           | 4                       | 186                | Rolling<br>shutter | 428        |

| JadePix3  | 16x23.11            | 3                       | 98.3               | Rolling<br>shutter | 370        |

- Advanced process to accommodate needed transistors within a pixel area  $< 400 \,\mu m^2$  (e.g. 16 x 25)

- 65 nm CIS process

- 200nm SOI + 3D integration

### **Device simulation (TCAD)**

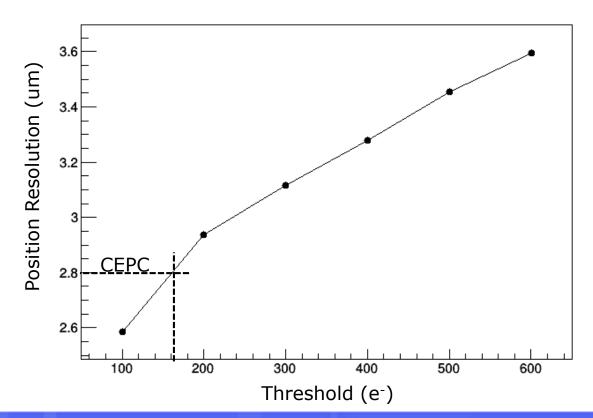

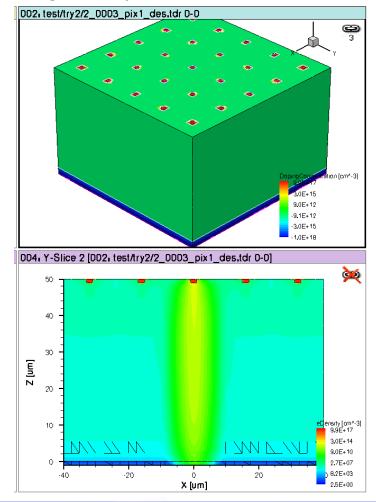

- Pixel pitch = 16 μm & Sensor thickness = 50 μm

- Low threshold is essential for the high position resolution

- Threshold < 200 e<sup>-</sup>

- ENC ~ 20 e<sup>-</sup>

#### Charge transportation in TCAD simulation

### Development of the CPV SOI pixel sensor

- Targeting on a **position resolution** ~ **3 um** and a readout scheme compatible with the proposed CEPC experiment

- CPV-1&2 for the study of position resolution of <u>small pixels</u> with simplified readout (FEE2018)

- CPV-3 for the study of <u>PDD sensing diode</u> (NIMA 1040 (2022) 167204)

- CPV-4 for the <u>3D architecture</u> (this talk)

2015.06

CPV-1

Process assessment

**Pixel size:** 16 μm × 16 μm

CPV-2

S.P. Resolution 2.3  $\mu$ m; Thinned to 75  $\mu$ m

Pixel size:

16  $\mu m \times 20 \ \mu m$

CPV-3

Pinned Depleted Diode; Optimized for low FPN 12 e<sup>-</sup>

Pixel size:

$17 \ \mu m \times 21 \ \mu m$

**CPV-4** Lower

3D architecture; Stacking process;

Compact Pixel for Vertex (CPV)

### **Outline**

- Introduction

- Challenges in vertex detector for future e<sup>+</sup>e<sup>-</sup> experiment

- Features of CPV-4 design and 3D-SOI process

- Sensing diode

- Analog/Digital separation

- 3D compatibility

- Verification of lower tier

- Reverse bias voltage

- Verification of upper tier

- Removal of handle wafer

- Verification of 3D integration

- connectivity

- Summary and Outlook

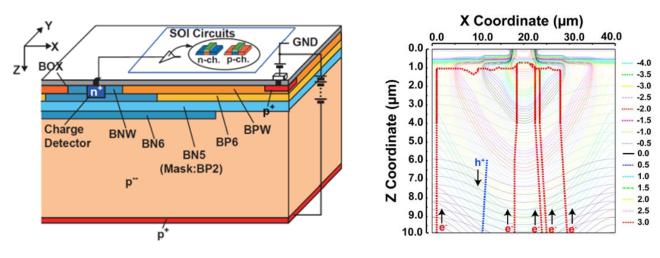

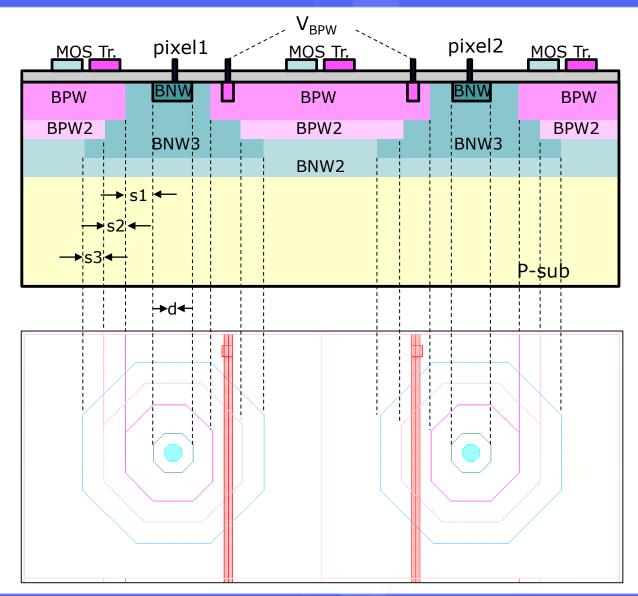

### PDD structure

- Improvement of sensing diode

- Pinned Si surface layer → reduction of <u>surface leakage</u> by 2 orders of magnitude

- Depleted charge collection electrode → reduction of <u>diode capacitance</u>

- Lateral electric field → improved <u>charge collection</u> efficiency

Proposed by Shoji Kawahito (Shizuoka U.) Ref: Sensors 2018, 18, 27; doi:10.3390/s18010027

- Pinned Depleted Diode (PDD)

- CPV-3&4 chip design

- Double-SOI

- CPV-1&2 chip design

- Nested-wells

- Buried P-Well (BPW)

Evolution of SOI detector process

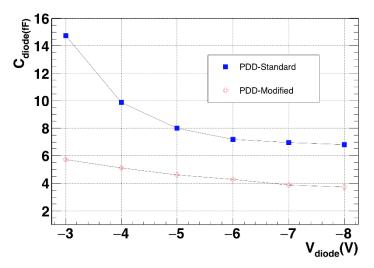

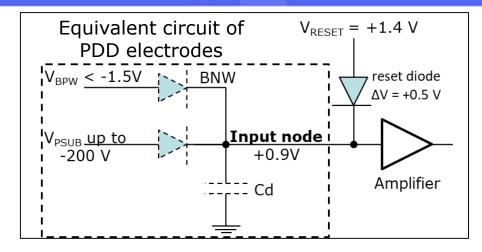

### CPV-4 sensing diode

- Geometry parameter optimized for small pixel pitch

- Indicated in the diagram as d, s1, s2, s3

| PDD type | d      | s1   | s2     | s3     |

|----------|--------|------|--------|--------|

| Standard | 2.8 µm | 2 µm | 1.5 μm | 1.5 μm |

| Modified | 2.8 µm | 2 µm | N/A    | N/A    |

- "Modified" has the BNW3/BPW2 removed

- Lower diode capacitance than PDD "Standard"

Diode capacitance measured on CPV-3 chip  $V_{diode} = V_{BPW} - V_{bnw}$  with  $V_{PSUB} = -20V$

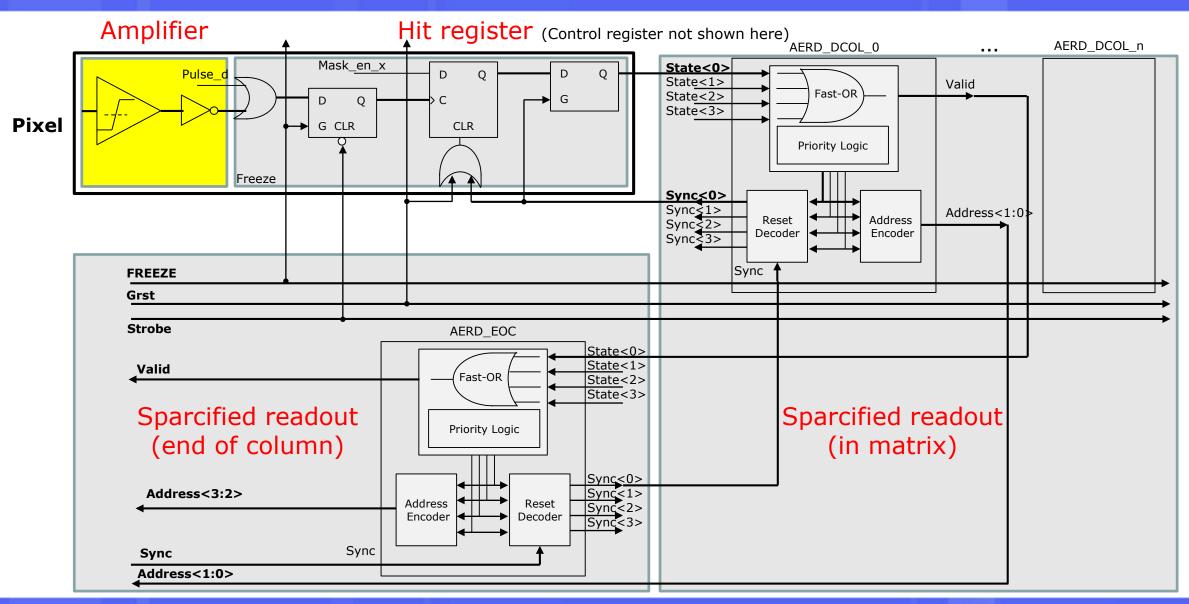

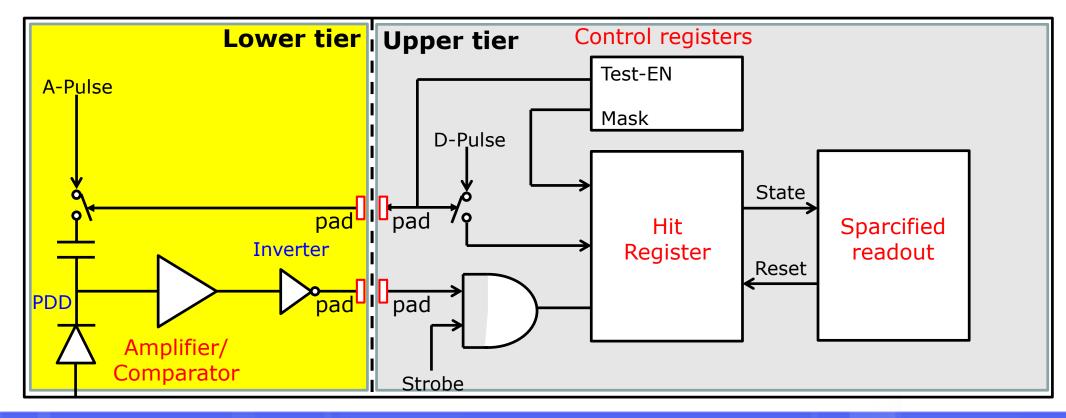

### **CPV-4 Pixel Readout Scheme**

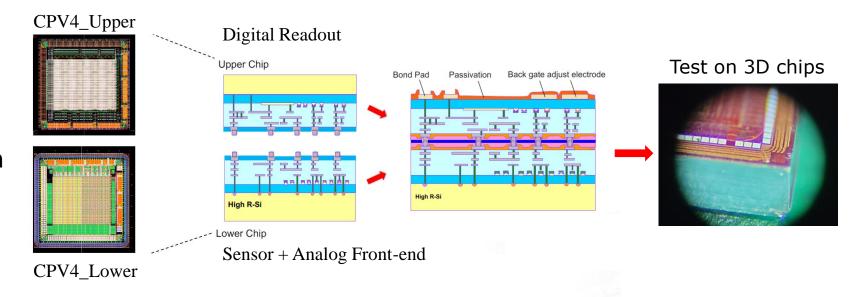

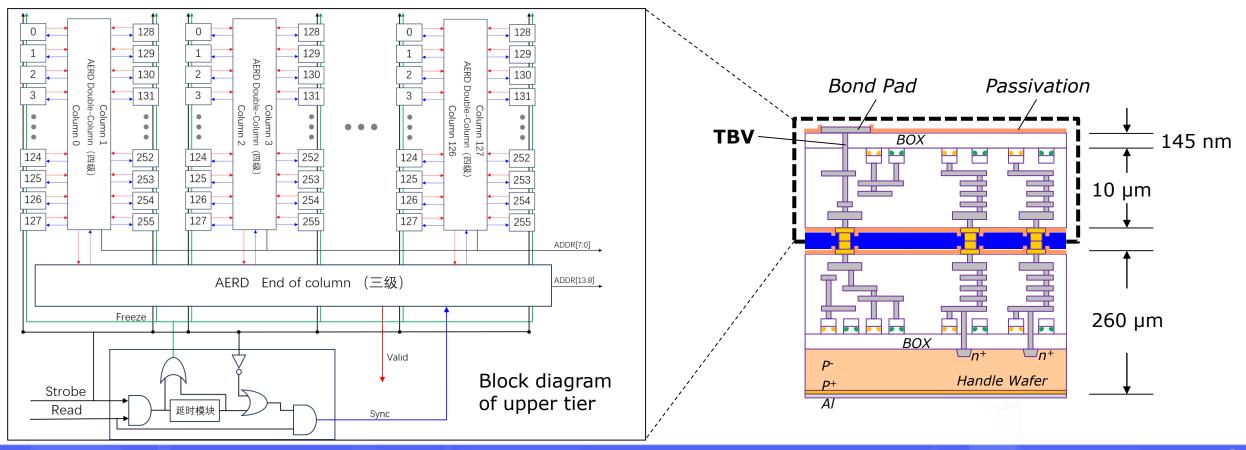

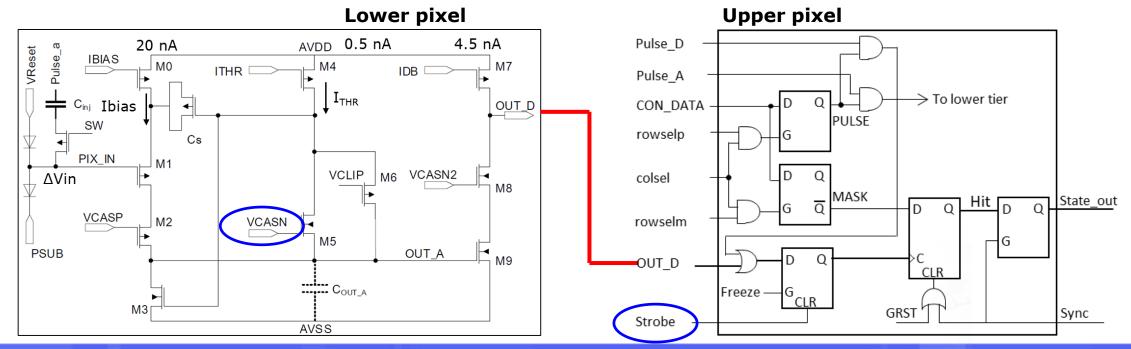

### Division of upper and lower functionality

- Lower tier: PDD sensing diode + amplifier/comparator

- Upper tier: Hit D-Flipflop + Control register + AERD readout

- **2 vertical connections** in each pixel: comparator output and switch of test pulse

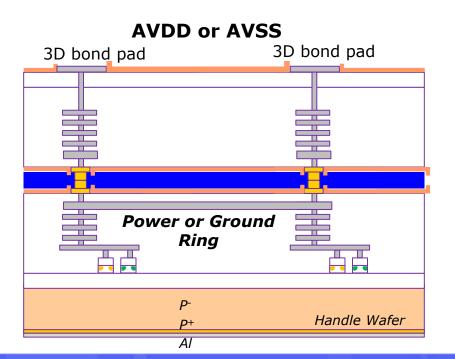

- Power and Ground are connected to the lower tier via the pad ring

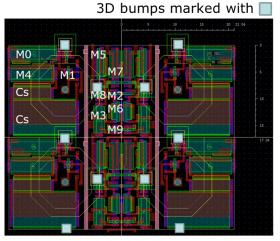

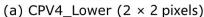

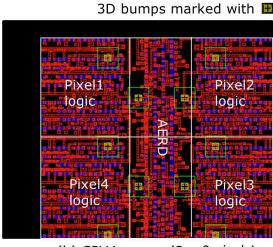

### **CPV-4 Matrix**

- 128 rows x 128 columns, divided into 8 sectors

- PDD standard vs simplified

- 2 variants of Front-end

- H-gate transistor to improve TID tolerance

- Pixel pitch 17μm x 21 μm

- Smallest pitch of similar design

- Pixel Area ~ 360 μm²

(b) CPV4\_upper (2 × 2 pixels)

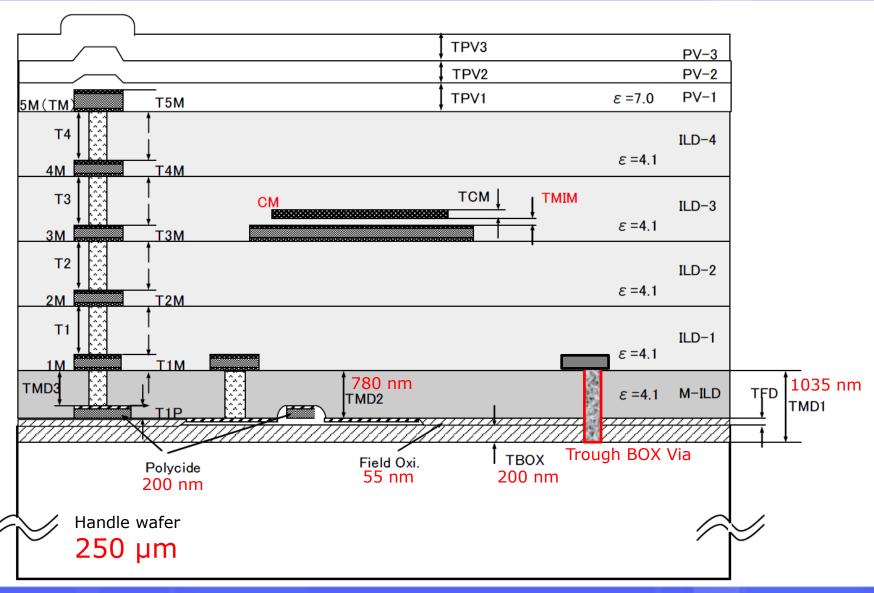

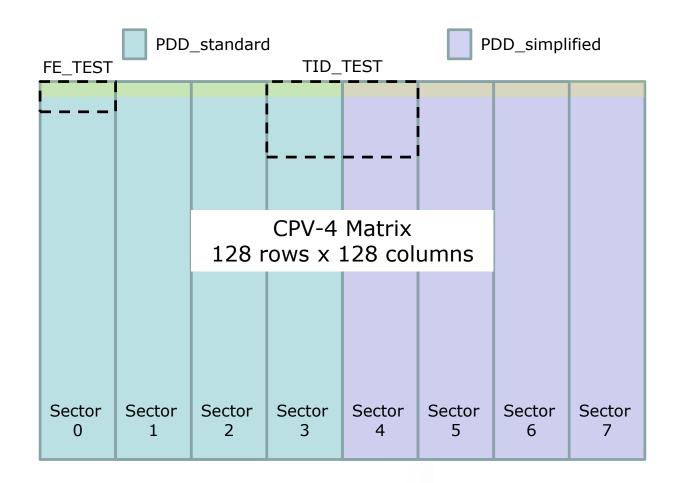

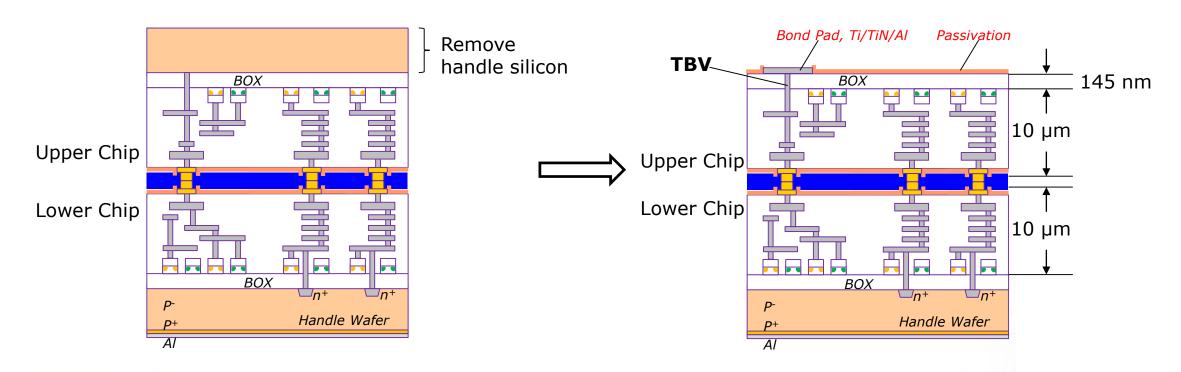

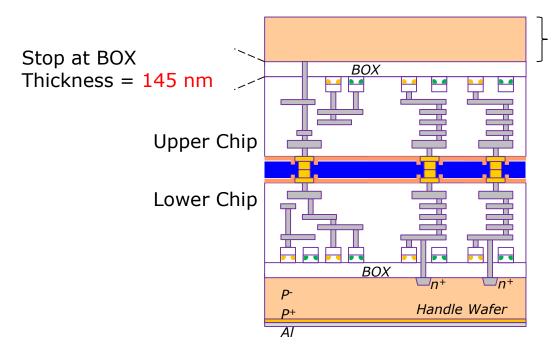

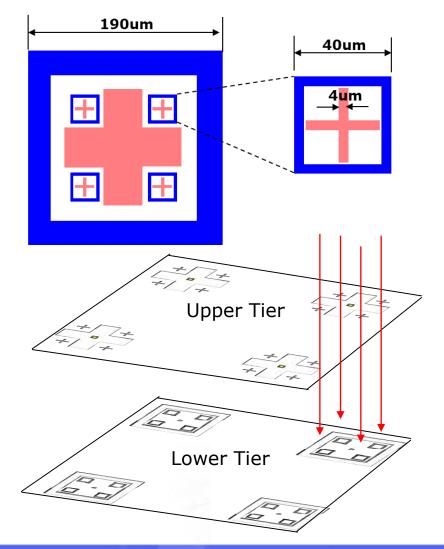

### 3D-SOI vertical integration

- Originally developed by T-micro and KEK

- Au bump, diameter  $\sim 3.5$  um, pitch  $\sim 7$  um, resistance  $0.3 \sim 0.4 \Omega$

- Multiple bumps in each pixel, for signals and (optional) power/ground connections

- Glue injection for mechanical strength

- Bond pads and passivation on top of BOX

### Compatibility between SOI and 3D

- Through Box Via (TBV) used for the bond pad connections

- The same type as the connection to the sensing diode

- Naturally a Via-first method

- Handle silicon of the upper chip removed precisely, reaching the thin BOX layer and exposing TBVs

- Wet etching stopped automatically by the Buried Oxide (BOX)

### **Outline**

- Introduction

- Challenges in vertex detector for future e<sup>+</sup>e<sup>-</sup> experiment

- Features of 3D-SOI process and CPV-4 design

- Sensing diode

- Analog/Digital separation

- 3D compatibility

- Verification of lower tier

- Reverse bias voltage

- Verification of upper tier

- Removal of handle wafer

- Verification of 3D integration

- connectivity

- Summary and Outlook

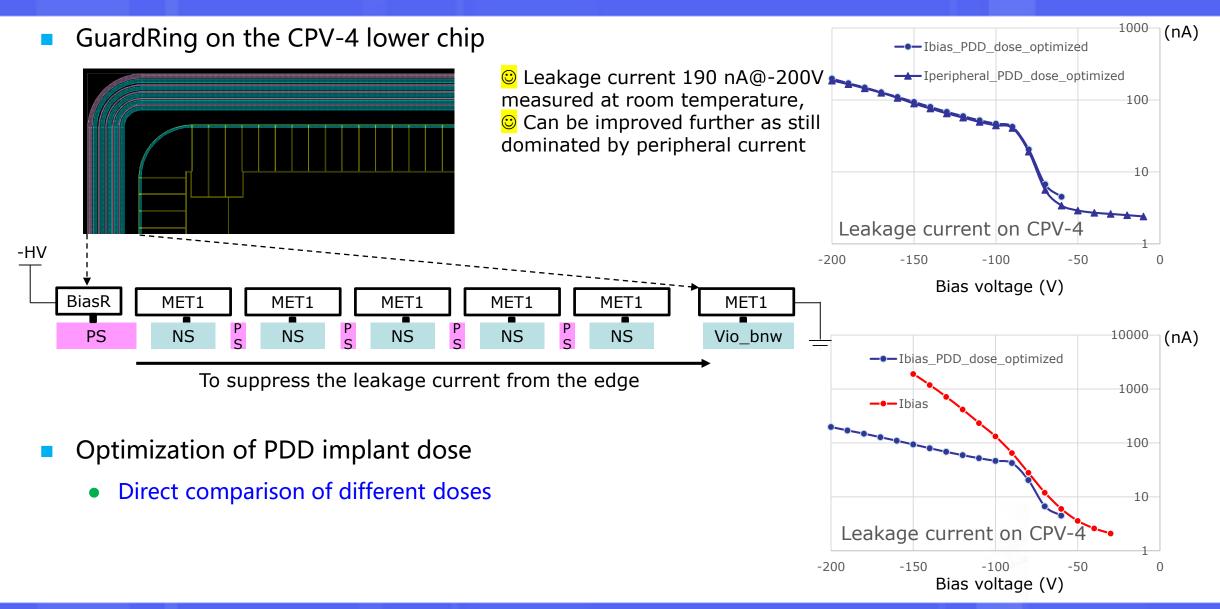

### Improvement of Leakage current

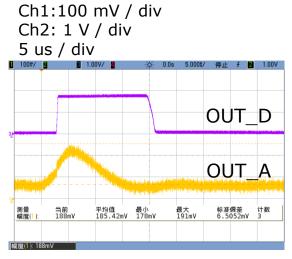

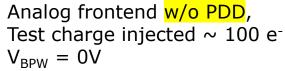

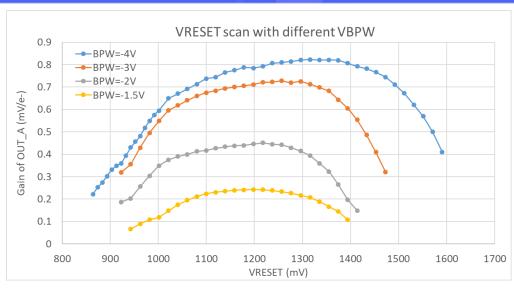

### **Electrical Pulse Test**

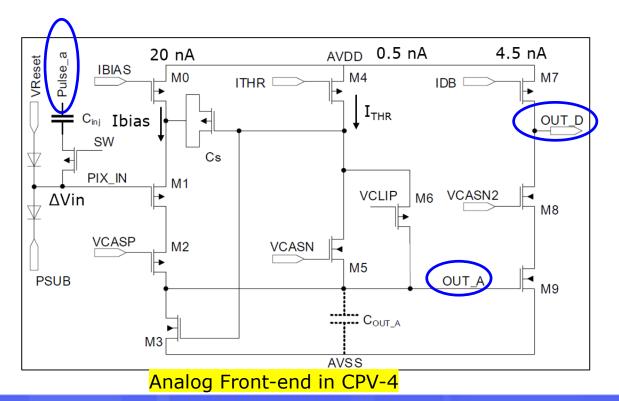

- Charge injection via C<sub>ini</sub> and Pulse\_a to Analog Front-end

- Observe waveform of test pixels on oscilloscope

- Reverse bias on V<sub>BPW</sub> is essential for PDD operation

- Minimum requirement: V<sub>BPW</sub> < -1.5V</li>

- Input node (V<sub>BNW</sub>) fixed to ~ +0.9V by V<sub>RESET</sub>

Ch1:100 mV / div

Analog frontend w/ PDD, Test charge injected  $\sim 750 \text{ e}^{-1}$  $V_{BPW} = -1.5V$

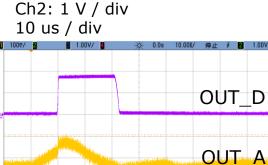

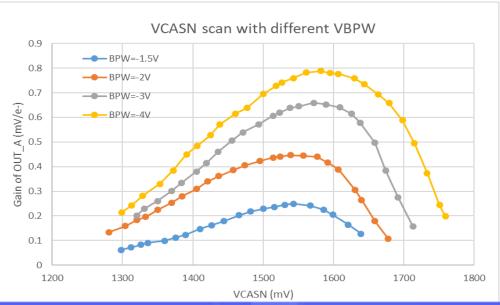

### Optimization of bias condition

- Transistor threshold shifted due to back-gate effect

- $\Delta Vt = k V_{back} (k \sim 0.02, V_{back} = V_{BPW})$

$$\Delta V_{t} = \frac{T_{GOX}}{T_{BOX} + \frac{\varepsilon_{OX}}{\varepsilon_{Si}} T_{SOI}} V_{back} = k V_{back}$$

- Circuit parameter scan with different V<sub>BPW</sub>

- V<sub>RESET</sub> setting the input node

- V<sub>CASN</sub> setting the OUT\_A node

- Gain of OUT\_A increased with V<sub>BPW</sub>

- Gain = OUT\_A\_amplitude / Input charge

- Benefitted from reduced C<sub>d</sub>

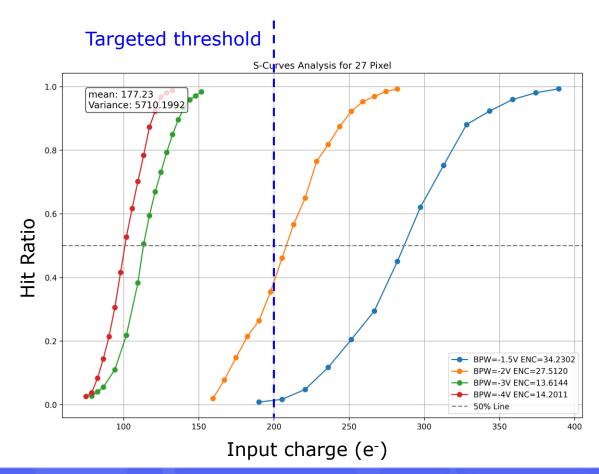

### S-curve Measurement

- Electrical pulse test

- Input-referred threshold decreased with V<sub>BPW</sub>

- ENC decreased with V<sub>BPW</sub>

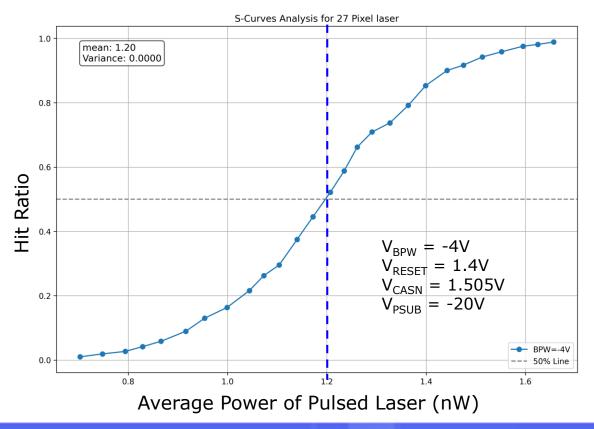

#### Infrared laser test

- Wavelength = 1064 nm & Pulse rate = 500 Hz

- Function of lower tier fully verified

### **Outline**

- Introduction

- Challenges in vertex detector for future e<sup>+</sup>e<sup>-</sup> experiment

- Features of 3D-SOI process and CPV-4 design

- Sensing diode

- Analog/Digital separation

- 3D compatibility

- Verification of lower tier

- Reverse bias voltage

- Verification of upper tier

- Removal of handle wafer

- Verification of 3D integration

- connectivity

- Summary and Outlook

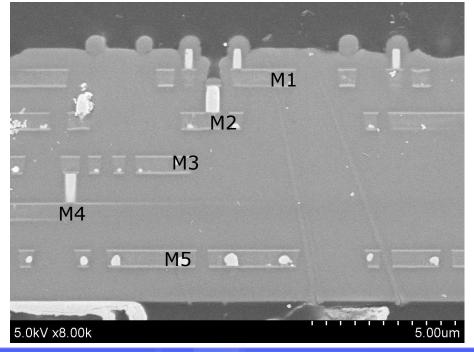

### Thinning of Upper tier

- Thinning of the upper tier is very delicate

- There is nothing but a thin BOX layer (200 nm) on top of the circuit

- Under-etching and Over-etching must be avoided

### Optimization of backside etching

- Low Resistive wafer is preferred for Upper chip because it is easier for WET etching

- But CPV-4 Upper chips are from the same <u>High Resistive wafer</u> as the Lower chips from

- Grinding (down to 20 μm) + dry etching to avoid over-etching

Remove handle silicon Thickness = 250 µm

#### Example of over-etching.

Passivation is not flat on cross-section SEM image

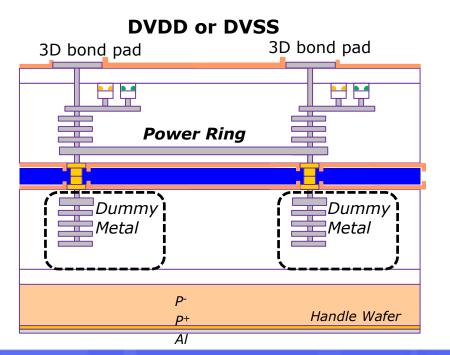

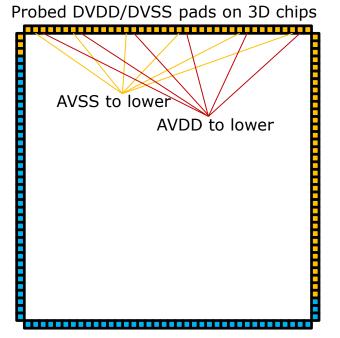

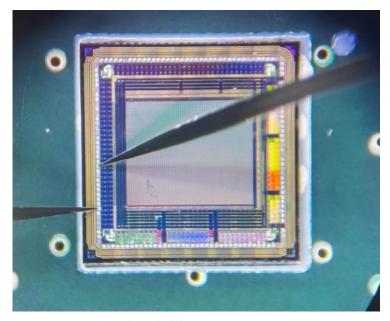

### Measurement of 3D connection to upper tier

- Probe test on the 3D chips: from 3D bond pad to the upper tier

- Measure the resistance between two power pads (DVDD) or two ground pads (DVSS)

- $2 \sim 6 \Omega$ , electrical connection established

- Yield 100% on 3 tested chips

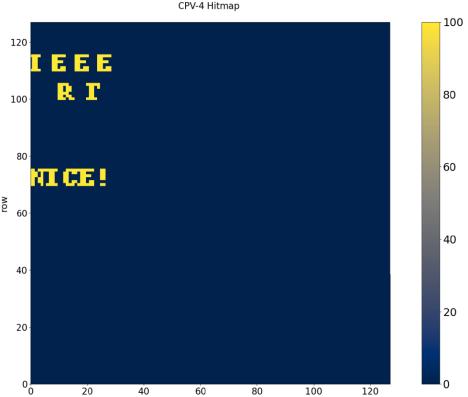

### Verification of Upper Tier functionality

- Readout of pixel hit by using digital test pulse as the stimulus

- Full matrix can be configured per pixel and readout correctly

Digital pixel logic in upper tier, with digital test pulse signal Pulse\_D and Hit output signal State\_out illustrated.

Hit map of the full matrix in digital pulse test, with character patterns illustrated. Number of test pulses = 100

### **Outline**

- Introduction

- Challenges in vertex detector for future e<sup>+</sup>e<sup>-</sup> experiment

- Features of 3D-SOI process and CPV-4 design

- Sensing diode

- Analog/Digital separation

- 3D compatibility

- Verification of lower tier

- Reverse bias voltage

- Verification of upper tier

- Removal of handle wafer

- Verification of 3D integration

- connectivity

- Summary and Outlook

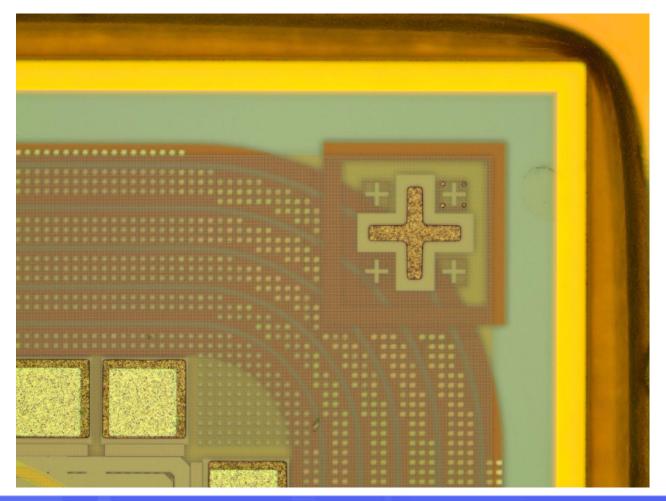

### Visual Inspection

- Chip to chip alignment confirmed on the cross marks, accuracy 1~2 um

- Dummy bumps can be seen aligned accurately

### Measurement of 3D connection to Lower tier

- Probe test on the 3D chips: from 3D bond pad to the lower tier

- Measure the resistance between two analog power pads (AVDD) or two analog ground pads (AVSS)

- $\sim 100 \Omega$ , contact resistance included

- 4 out of 6 tested chips are good

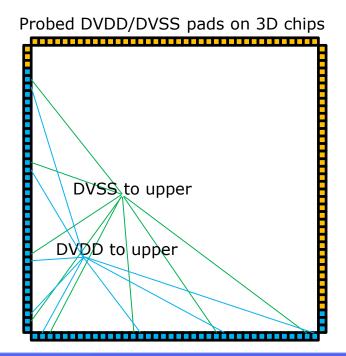

### Test of pixel connection

- Each pixel has an OUT\_D connection between lower and upper tier

- Tuning V<sub>CASN</sub> to define the state of OUT\_D (1 or 0)

- Generate HIT = OUT\_D & (!Strobe) by Strobe pulse

- Connectivity is checked by assigning OUT\_D = 1

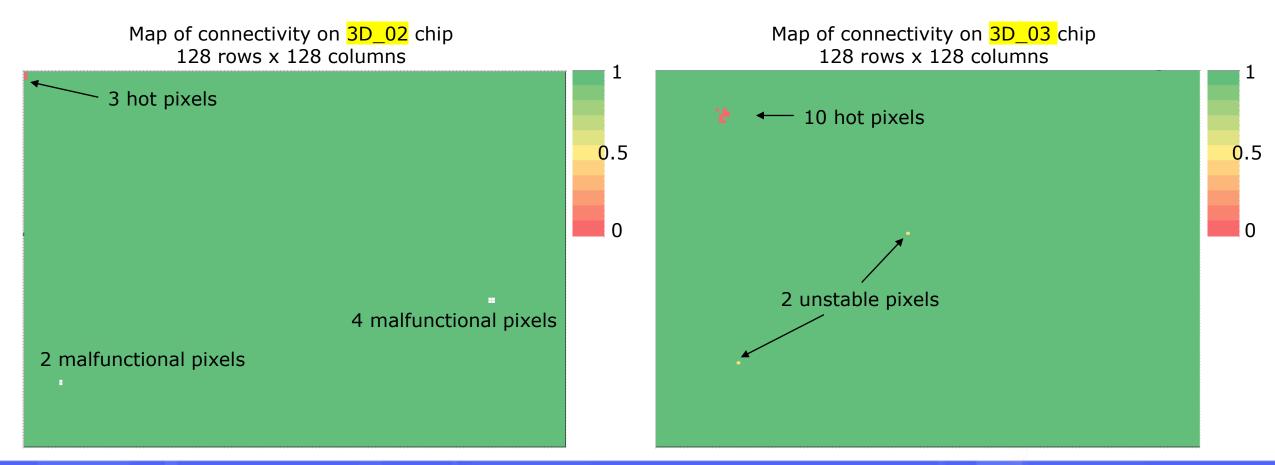

### Connectivity of pixel matrix

- Yield of pixel connection ~ 99.9%

- Small cluster of hot pixels with HIT = 1 even when OUT D = 0

### Summary and outlook

- 3D chip-to-chip bonding being pursued for high granularity

- Compatible with the existing SOI process

- First trial of CPV-4 finished

- Established full chain of sensing and readout functions

- Critical points verified successfully

- Reverse bias voltage on analog frontend

- Thinning of handle wafer

- Vertical connectivity with micro bump bonding

- A short-circuit issue between V<sub>BPW</sub> and AVSS is found in recent 3D chips

- Investigation is underway

- Samples from the same wafer have been identified and will be analyzed

### Acknowledgement

- The SOI pixel detector and 3D bonding process have been developed in the framework of SOIPIX collaboration. The authors thank all the collaborators, especially Ikuo Kurachi, Chiharu Ichitsubo, Makoto Motoyoshi, Miho Yamada and Yasuo Arai.

- This work is supported by the National Natural Science Foundation of China under grant number 11935019, 11575220.

## Thanks for your time!

Backup slides

### A survey of high position resolution

### Stackup of layers in SOI pixel process