## Q-RadSemi2026

Driving the Space Computing Power Innovation by

DIOS(Dependability Improvement Technology on Orbit Server System)

23 Jan., 2026

CONFIDENTIAL - COMPETITIVELY SENSITIVE INFORMATION

This document contains confidential and competitively sensitive information that is intended only for the recipient.

Unauthorized disclosure, copying, or distribution is strictly prohibited and may result in legal action.

## Speakers

### Inventor of DIOS Technology

SPACEBLAST

**Yoshifumi Sakamoto, Ph.D, PMP**

Chief Technology Officer

SpaceBlast

### Business Lead of DIOS

Mitsubishi Corporation

**Kazuma Murakami**

Project Manager of Commercial Space Station

Mitsubishi Corporation

## Company Overview

### Mitsubishi Corporation

|                      |                               |

|----------------------|-------------------------------|

| Date Established:    | July 1, 1954                  |

| Number of Employees: | 4,477<br>62,062(Consolidated) |

| Net Profit*:         | USD 6.4 Bn                    |

| Total Assets*:       | USD 155 Bn                    |

| Equity*:             | USD 60 Bn                     |

(\*) Figures are quoted from FY24 Financial Result. All numbers are USD.

## MC Defense and Aerospace

- Contributing to society and national security through Defense and Aerospace business

- In the space business, we are committed to business development with the purpose of solving industrial challenges on Earth through the provision of valuable space outputs for the planet.

- In dual-use business, we combined and utilize the network developed in our defense business and MC's broad industrial interface to achieve the commercialization of dual-use technologies that have a significant impact on society.

### Defense Business

- Acting as a representative for U.S. defense industries such as Lockheed Martin, Raytheon, MC propose products and solutions that align with the strategies of the Japan Ministry of Defense and domestic J-industries. MC also conduct intelligence activities, including monitoring the trends of other countries.

- MC ensures the execution of contracts, including individual contract agreements, process and delivery in timely manner.

### Space Business

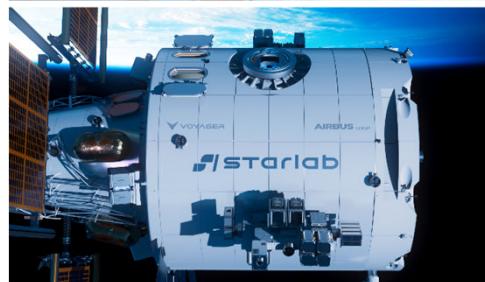

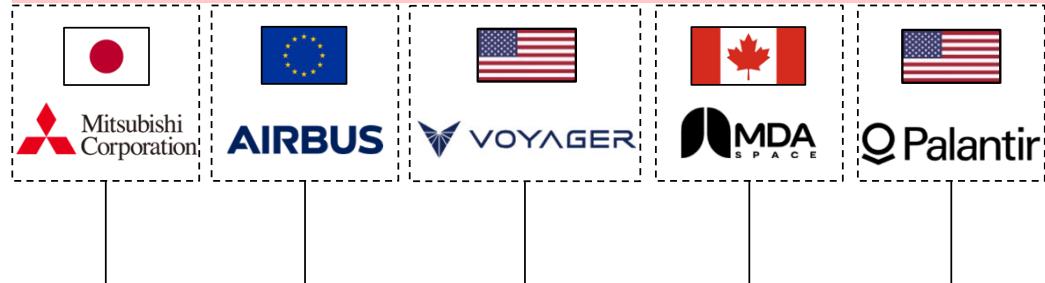

- Starlab: Promote Commercial LEO Destination (commercial space station) business as strategic equity owner of Starlab Space LLC, a global joint venture with Voyager Space, Airbus, and MDA.

- Japan Space Imaging Corporation(JSI): Established JSI in 1998 to distribute satellite imagery in Japan as a pioneer, partnering with US companies.

- Astroscale: Invested in Astroscale, who has cutting-edge space debris removal technology.

### Dual-use Business (Robotics/AI)

- Leveraging our network with the U.S. DoD and U.S. industries, MC envision business that contribute to solving social and industrial challenges with utilizing advanced technology.

- In addition to our expertise in business for the Japan Ministry of Defense, MC aim to realize the civilian application to enhance and expand MC's broad range of business activities.

## Commercialization of Space

Private-led growth is accelerating space innovation and creating value across non-space industries

### (Past) Government Driven

### (Present/Future) Private Driven Commercialized Assets

Satellite

Communication

Rocket

Observation

Satellite

Price

User

Service

Use

Case

Industrial

Structure

Design

Philosophy

Innovation

Contribution to Non-Space Industry

## — (Our Challenges) The Last Commercialization Asset Remaining in LEO/Space Station

- Starlab is the candidate of NASA / Commercial LEO Destination ("CLD") Program.

- It is necessary to transform the culture, rules, and business model of the space industry to adapt to the changing market structure, shifting from government-driven to commercial.

- By leveraging MC's diversified business portfolio, MC aims to lead innovation through Commercial Space Station.

### Starlab Space Partnership

- MC has participated in Starlab as Equity Owner and Strategic partner.

- MC dispatches a director and a secondee to Starlab

#### Joint Venture Shareholders (Strategic Partners)

## Potential Japan-led Game-Changing Projects with Global Ambitions

Refer to next page

### Space x Semiconductor

Microgravity for

Next Gen Semiconductor Technology Development

Innovation

High Quality Seed Crystal Yield Rate Improvement Technology

### High Dependability Computer

Space Station for

Space Cloud Computing Service Platform

Innovation

Innovative Dependability Technology

High Performance, Low Power computer for AI Implementation

### Space x Life Science

Microgravity for

3D Organoid for Drug Discovery

Nanomaterial for Drug Delivery

Innovation

High-extrapolation models with iPS Cell

Advanced Drug Delivery System

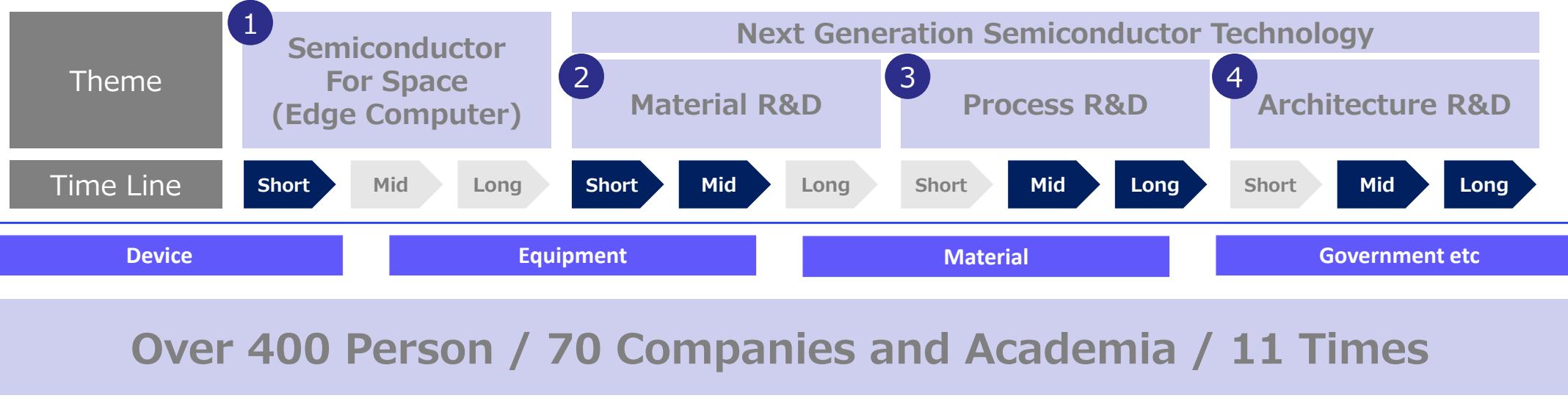

## Space Semiconductor Workshop

- MC initiated the workshop with Semiconductor companies. (11 Times / Total 400 Person and 70 Companies and Academia)

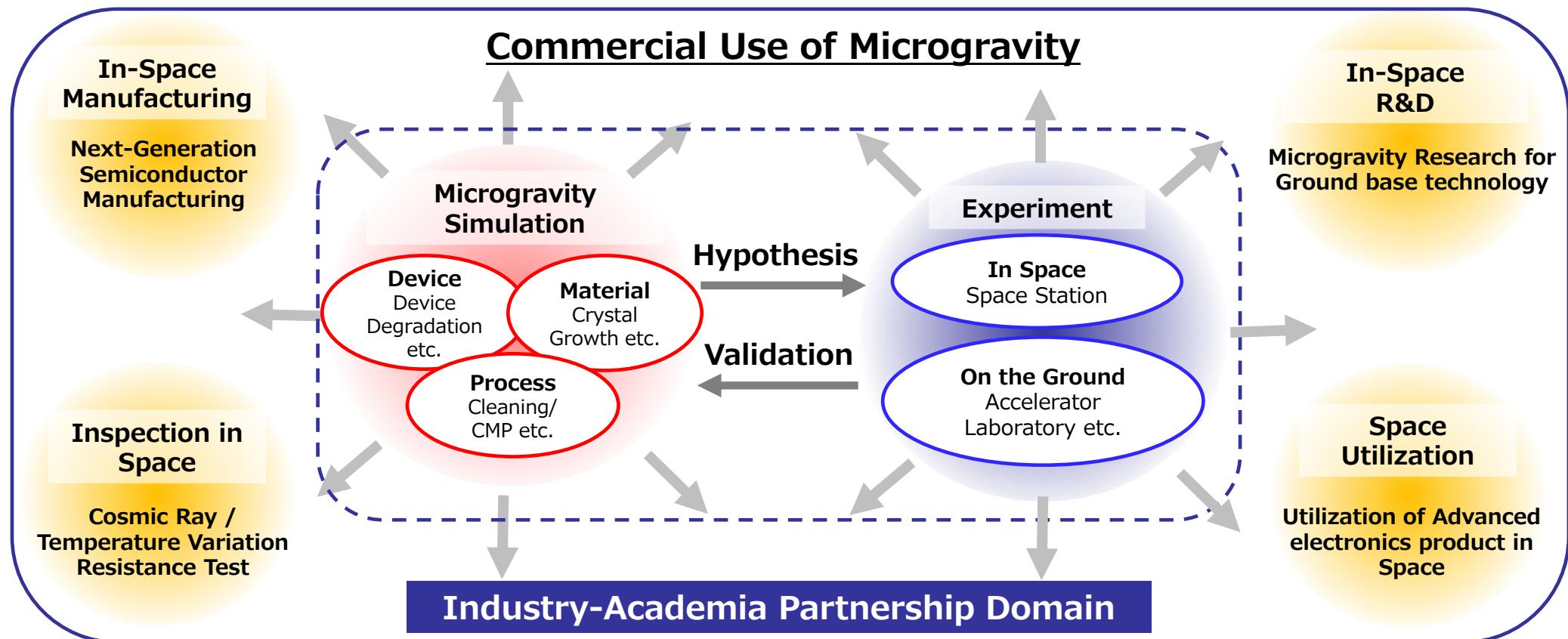

## Microgravity for Next Generation Semiconductor Technology

- Discussions are ongoing with Japanese Semiconductor related companies to explore innovation opportunities leveraging microgravity environment

- As a first step, we are advancing efforts to validate the effectiveness of microgravity through a combination of simulation development and experimental implementation

## Today's Topics / Our Products (DIOS / Open Orbit)

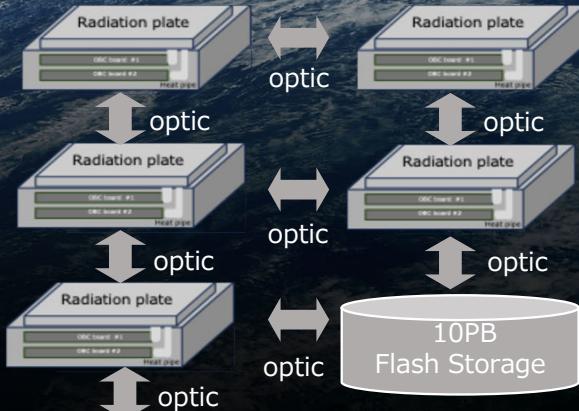

### DIOS ( High Dependability Edge Computer )

#### Core Unit

Two OBC boards in a single Core unit

160mm x 170mm x 120mm

(without radiation plate)

#### Scalable Design

Space Station

### Open Orbit ( Space Cloud Computing Service )

#### Orbital Data Center (ISS / CLD)

- LLM Learning and Execution

- Multi-System Monitoring

- Remote Management

- Archive

#### EO-SAT

- Image Analysis

- Construction of an Orbital Network

#### Zone Data Center

- Remote Management

- Archive

- LLM execution

#### SATCOM

- Image Analysis

- Construction of an Orbital Network

#### Ground DC

- Data Integration Platform

- LLM Training

- Multi-System Monitoring

- Remote Management

- Archive

AI Model Updates

Software Management

Archive

# Q-RadSemi2026

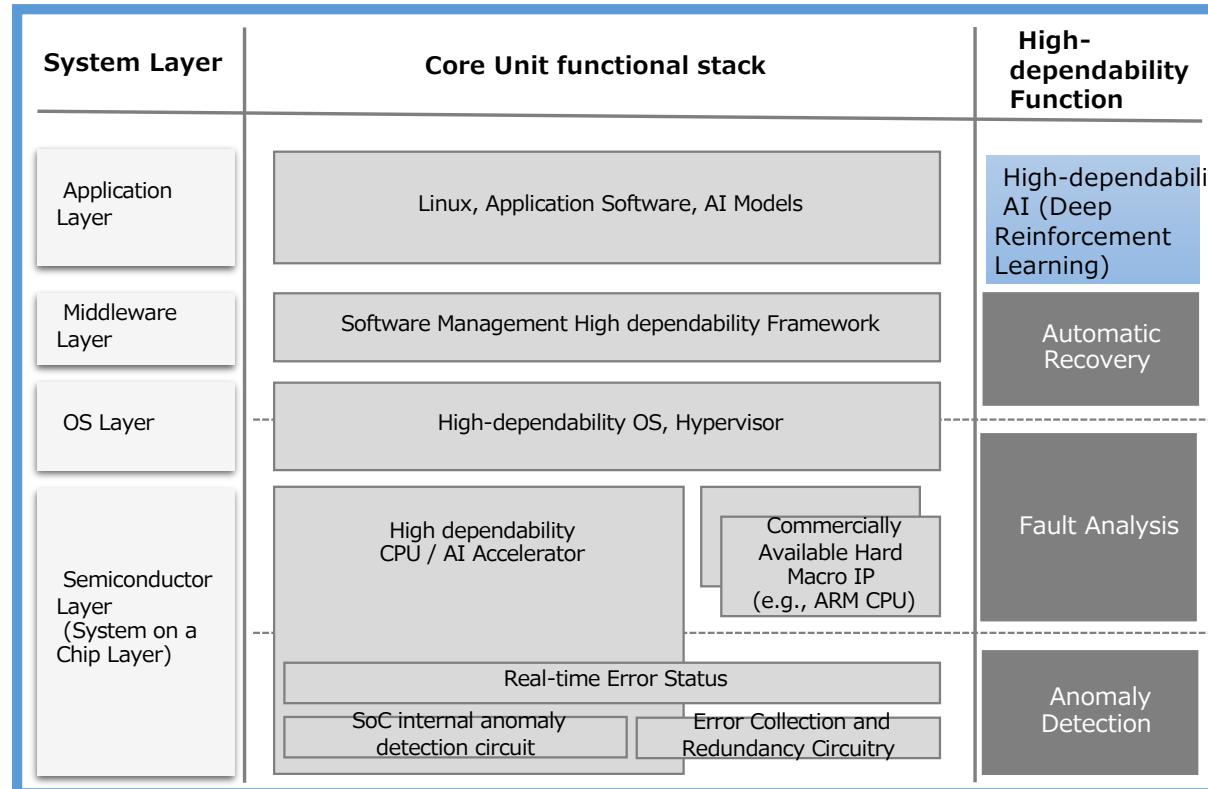

## Overview of DIOS

- Dependability Improvement Technology on Orbit Server System

## Overview of This Proposal: Deploying DIOS Technology as a Core Solution for the OpenOrbit Business

- Integrating innovative technologies into compact data centers

- Delivering new business models to Japan and the world

### DIOS Dependability Improvement Technology on Orbit Server System

Full-stack solution of Aggressively adopt high-dependability Semiconductor, Software and AI technology trends across multiple domains

#### ● High-dependability hardware

- High-dependability CPU: RISC-V HD (High Dependability)

- High-dependability AI Accelerator: AI Engine HD

- MP-Soc (Multi-Processor System on a Chip) configuration suitable for both application and real-time uses

#### ● High-dependability Software

- Virtualized Linux running on a high-dependability framework

- High-dependability real-time OS and real-time hypervisor

- Early adoption of high-dependability technology meeting next-generation autonomous vehicle functional safety requirements (ISO 26262)

#### ● AI-Based System Resource Control

- Achieves high dependability, high energy efficiency, and low heat dissipation through AI-based control of dependability functions and system resource management

- Utilization of reinforcement learning-based AI

- Integrated control via autonomous AI - Operational range restricted for safety assurance

#### High-dependability Data Center Essential Requirements

- High Availability (Uptime) Redundancy and data sharing

- Highly Reliable System Architecture Clustering and Load Sharing

- Cluster system monitoring Failure Detection, Analysis, and Recovery

- Load Sharing Load Balancers and Service Monitoring

- Server Virtualization Hypervisor-based Energy Efficiency Improved energy efficiency, effective resource utilization through AI, Utilization of open-source assets

Business Strategy for Building an Orbital Cloud

Connecting Everything

### OpenOrbit - Space Cloud Service

#### On-Orbit Data Center (ISS / CSS)

Optical communication or Ku/Ka band

Observation Satellite

Medium/Small

Optical communication or Ku/Ka band

Zone Data Center

Medium-sized/Dedicated

Optical communication or Ku/Ka band

Communication Satellite

Medium/Small

Optical communication or Ku/Ka band

API Integration (Ku/Ka-band)

Ground Data Center

Control, AI Training, Software-Defined

Internet

Ground-based Cloud

Space operators (LCD, satellite, etc.) and hyperscaler integration

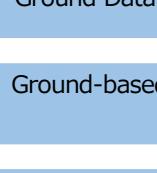

# Current Market Situation and Challenges: Computing Capability in Space Cannot Meet Demand

What is required of an orbital data center?

High-density computing capabilities equivalent to ground-based data centers meet demand

## ● Risks in the Near Future

As is, we cannot meet the demand.

Computing Capability in space increases dramatically. AI workloads rise sharply, but satellite launches only double.

## ● The need for timely service deployment

**Low-Cost, fast, open**

- Achieving High Functionality Using technology trends across multiple domains

- Low-cost Development, Operation, and Services Utilizing Consumer Technologies

- Achieving horizontal specialization through the adoption of open technologies and open strategies

## ● Client Feedback: Current Issues

**Expensive, slow, closed**

Strong sense of urgency in the business domain

- Every component—hardware, communications, operations—is expensive.

- “Closed” technology systems place unspoken barriers to market entry, resulting in computing capacity that is several times to a hundred times smaller. This significantly impacts crew costs.

- Slow development

# Challenge

## Full-Stack approach for high-dependability

- High-dependability functions implemented in semiconductors using logically synthesizable circuits.

- Adoption of a software stack meeting functional safety standards of Automotive.

- System-wide monitoring and control via AI - AI orchestration.

- Not dependent on semiconductor materials or specialized circuits.

- Not dependent on specific fabs or technology nodes.

- Leverage widely available consumer technologies.

## Technical and economic objections in dependability

- SOI technology is highly resilient to radiation effects, but there are no plans to apply it beyond the current leading-edge process nodes.

- Dependence on specific semiconductor processes or fabs significantly limits its medium-to-long-term usability.

- Certain materials and specialized circuits (analog, logic circuit cells) become extremely expensive, making their use impossible at a realistic price range.

# Full-Stack approach for high-dependability

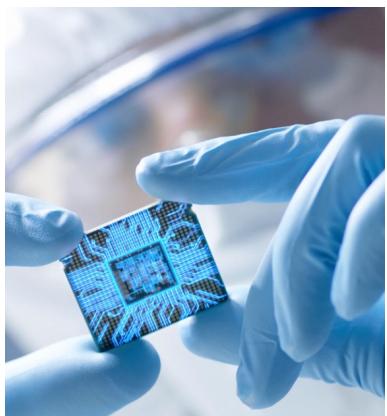

- The “core unit” consists of two OBCs(On-board computer), forming the smallest unit in a data center

- Multiple core units are clustered together to form a data center

- The core unit's high-dependability technology widely utilizes technologies from semiconductors to AI in a Full-Stack approach

## CoreUnit - System Architecture

## Data center performance

Data center total

CPU 2,388.0 KDMIPS

AI 369 TOPS

TPD 400W

# System Architecture Foundational to the Full-Stack Approach

Achieving high availability (uptime) in data centers

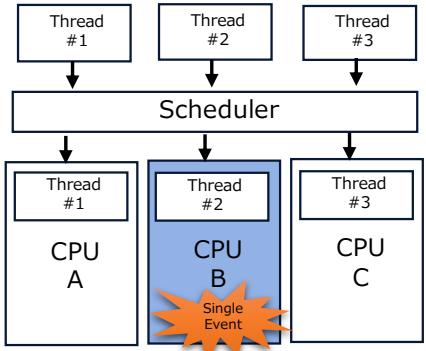

## ● Multi-CPU architecture adopted by DIOS

Software Node distribution and load balancer migrate processing to another CPU

**Long** : MTBF

(Mean Time Between Failures)

**Short** : MTTR

(Mean Time to Repair)

It is easy to identify the target thread (software) from the source of the error

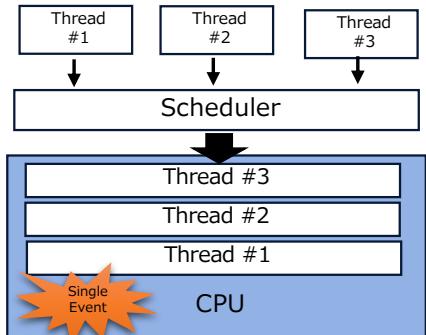

## ● Conventional single-CPU architecture

System reset and restart

**Short** : MTBF

(Mean Time Between Failures)

**Long** : MTTR

(Mean Time to Repair)

It is difficult to identify the target thread from the source of the error

The ability to detect the occurrence of a single event is of critical importance.

In a single-CPU system, determining which software is affected when a single event occurs is extremely difficult. However, in a multi-CPU system, if the CPU where the single event occurred can be identified, the affected software can be easily pinpointed.

## Fundamentals of System Architecture

- Heterogeneous or homogeneous multi-CPU hardware.

- Software is dedicatedly assigned to individual CPUs.

- Software running on CPUs or accelerators is each loosely coupled.

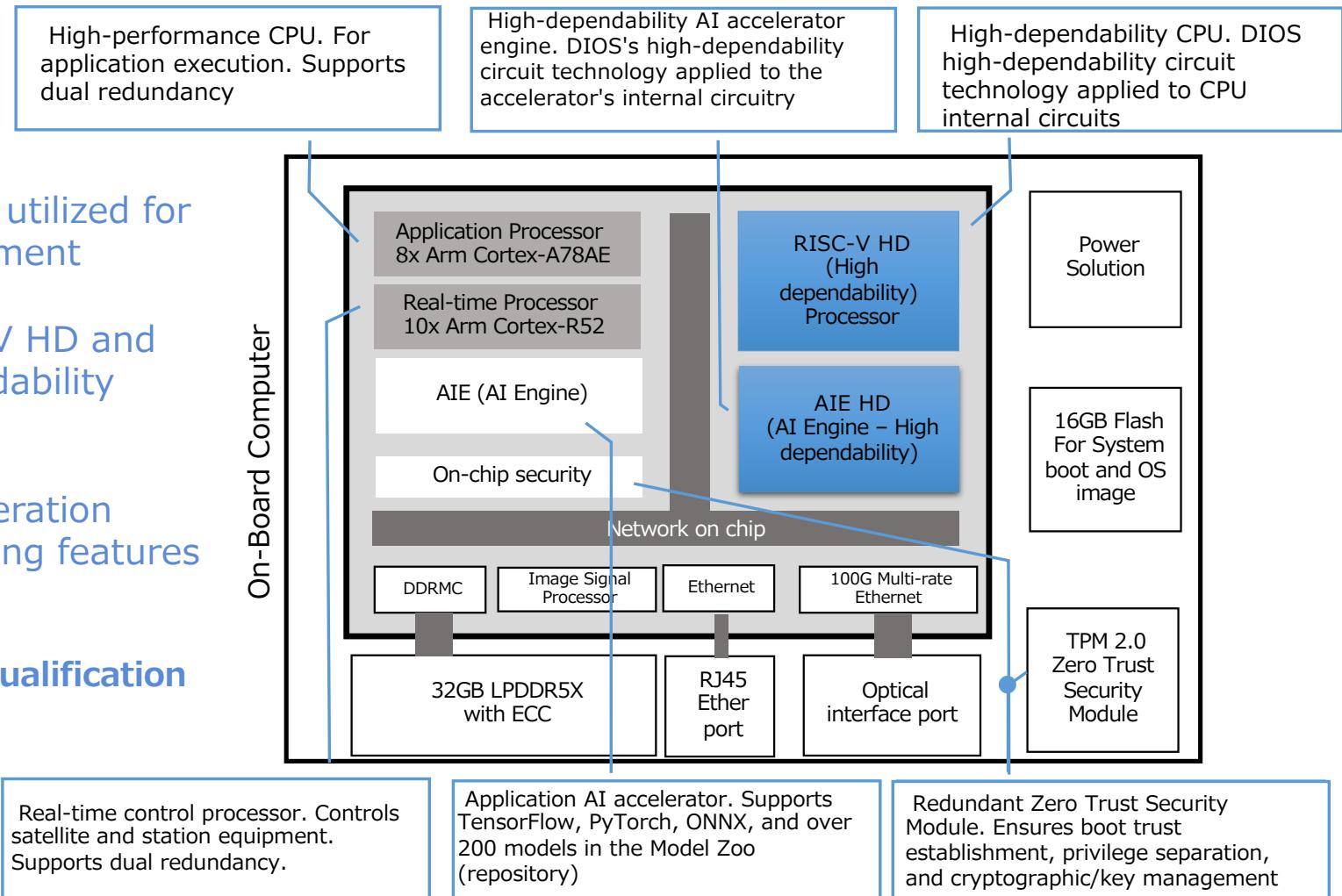

# DIOS Hardware architecture

## High Performance FPGA and High dependability IPs

- Multiple CPUs redundantly utilized for each application and equipment control in the data center

- The newly developed Risc-V HD and AIE HD handle high-dependability functions

- Dynamic control of energy consumption and heat generation through diverse power-saving features

Xilinx AI Edge GEN2,

**2029 - Class B and Class Y qualification**

# Radiation-resistant semiconductor technologies

## Radiation resistance achieved through architecture and high-dependability technologies

- Achieved through DIOS's high-dependability architecture—cannot be realized by any single technology alone

- By utilizing semiconductor circuits as "sensors," error detection previously impossible becomes achievable

- Overcomes inherent weaknesses of the latest technology nodes and FPGAs

| Error Countermeasures for DIOS / Effects of Space Radiation Environment | Error Detection and Mitigation Technology                                                     | Target                                                                                                                                                                                      | SEU (Single Event Upset) | SET (Single Event Transient) | SEFI (Single Event Functional Interrupt) | SEL (Single Event Latch-up) | SEB (Single Event Burnout) | TID (Total Ionizing Dose) | DDD (Displacement Damage Dose) |

|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------------|------------------------------------------|-----------------------------|----------------------------|---------------------------|--------------------------------|

| <b>Memory Error Correction</b>                                          | ECC and Scrubbing Mechanism                                                                   | DRAM and FPGA circuits incorporate LUT (Look Up Table) distributed RAM, Block-RAM, Ultra-RAM                                                                                                | ✓                        | ✓                            | ✓                                        | -                           | ✓                          | -                         | -                              |

| <b>Combination Circuit Error Countermeasures</b>                        | Dual redundancy or triple redundancy                                                          | Dual redundancy: ARM CPU<br>Triple redundancy: AI Engine (internally divided into three sections), RISC-V HD, AI Engine HD                                                                  | -                        | ✓                            | ✓                                        | ✓                           | ✓                          | -                         | -                              |

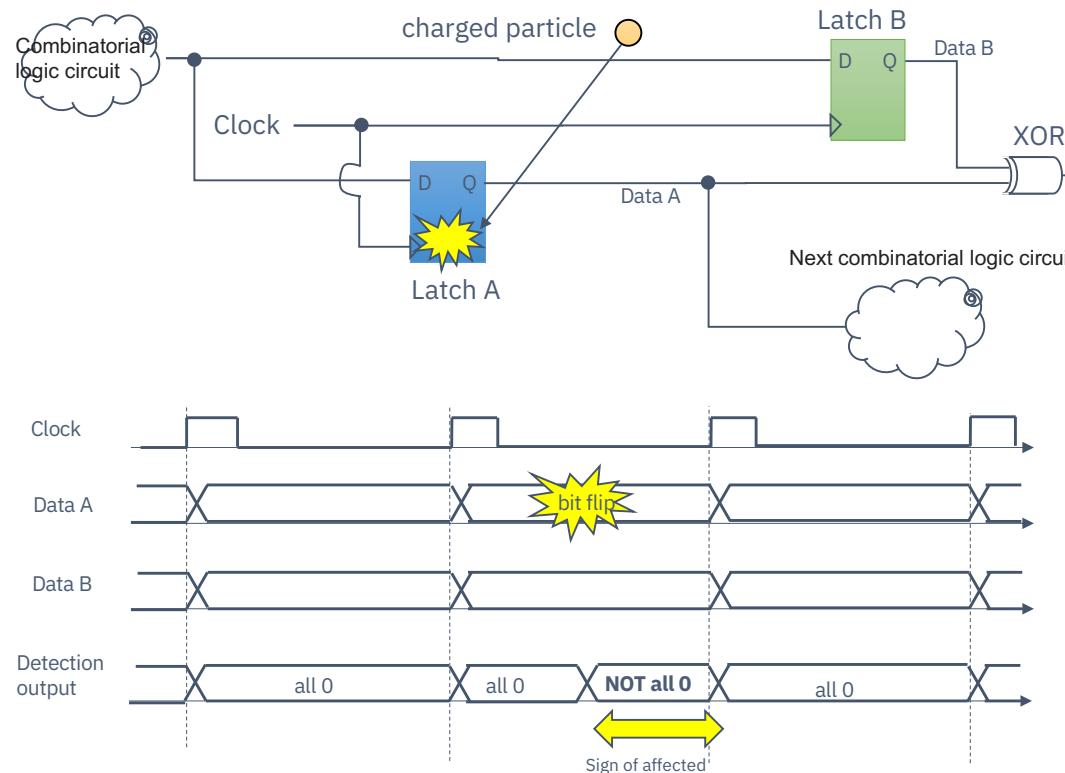

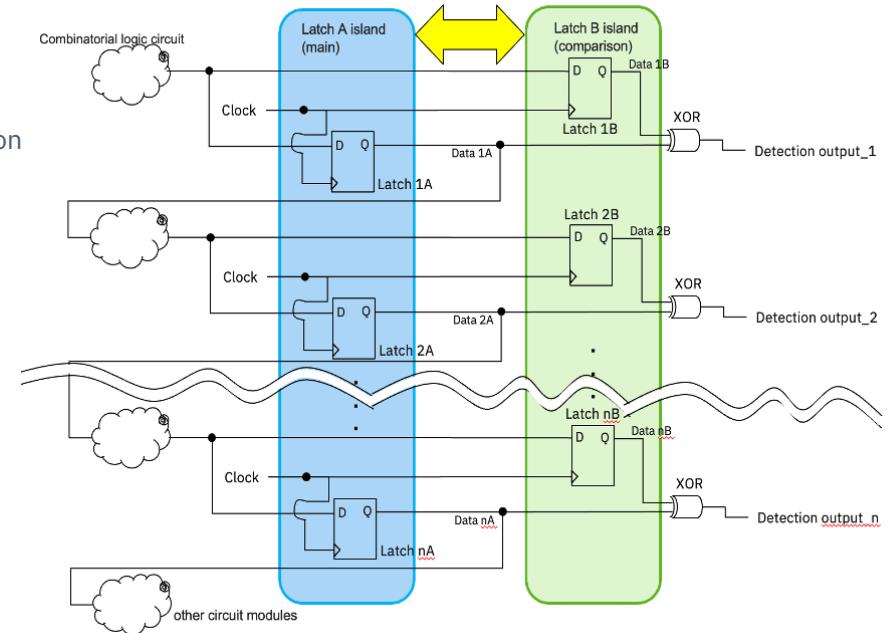

| <b>Latch circuit Error countermeasures</b>                              | Detection via output comparison of two physically separated latches                           | Circuits within RISC-V HD that are small in scale yet significantly impact CPU or AI accelerator operation, such as majority voting functions, error detection circuits, and register files | ✓                        | ✓                            | ✓                                        | ✓                           | ✓                          | -                         | -                              |

| <b>CRAM Error Handling</b>                                              | ECC and Scrubbing Mechanism                                                                   | CRAM (Configuration RAM). SRAM specific to FPGAs. Stores configuration information for programmable circuits.                                                                               | -                        | -                            | ✓                                        |                             | ✓                          | ✓                         | ✓                              |

| <b>Detection of heavy particle collisions and neutron showers</b>       | Equipped with a sensor mechanism for locating the point of origin within a semiconductor chip | Entire programmable area                                                                                                                                                                    | -                        | -                            | ✓                                        | -                           | ✓                          | -                         | -                              |

# Latch circuit Error countermeasures - Detection method of Single event upset of latch

- Prepare a comparison circuit that performs equivalent operations to the main circuit. Continuously compare values to detect SEUs.

- To prevent both the main circuit and comparison circuit values from inverting during a single SEU (to prevent malfunction), physically place them on the chip with a gap between them.

- Add one more one latch circuit for real time error collection.

Latch A Island and Latch B Island should be physically spaced apart

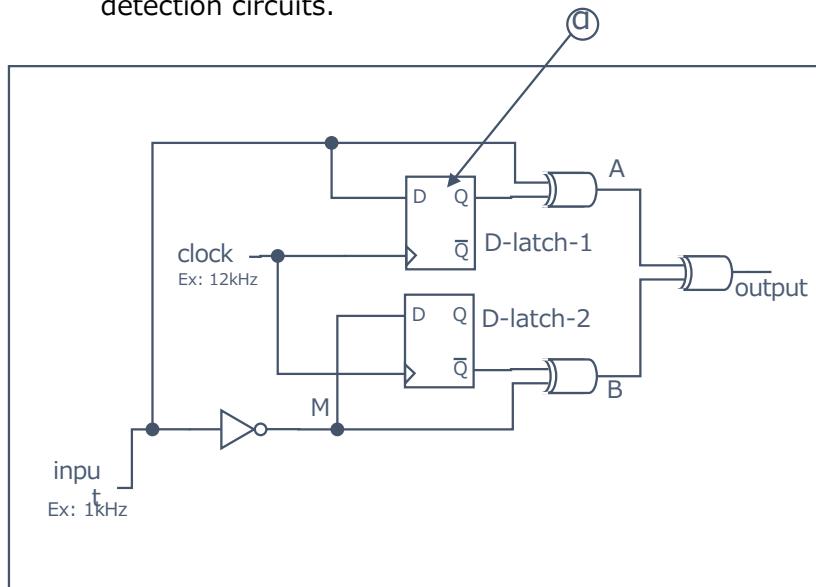

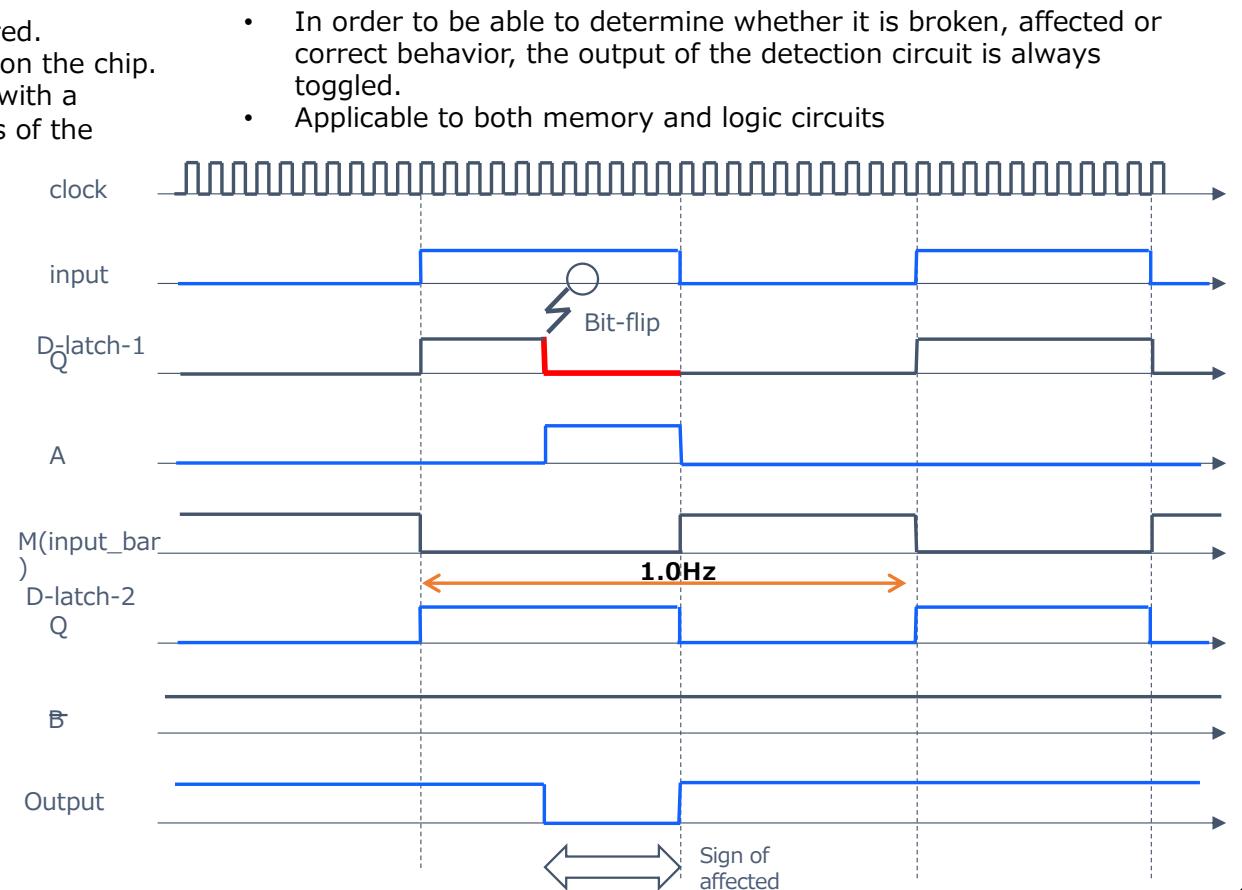

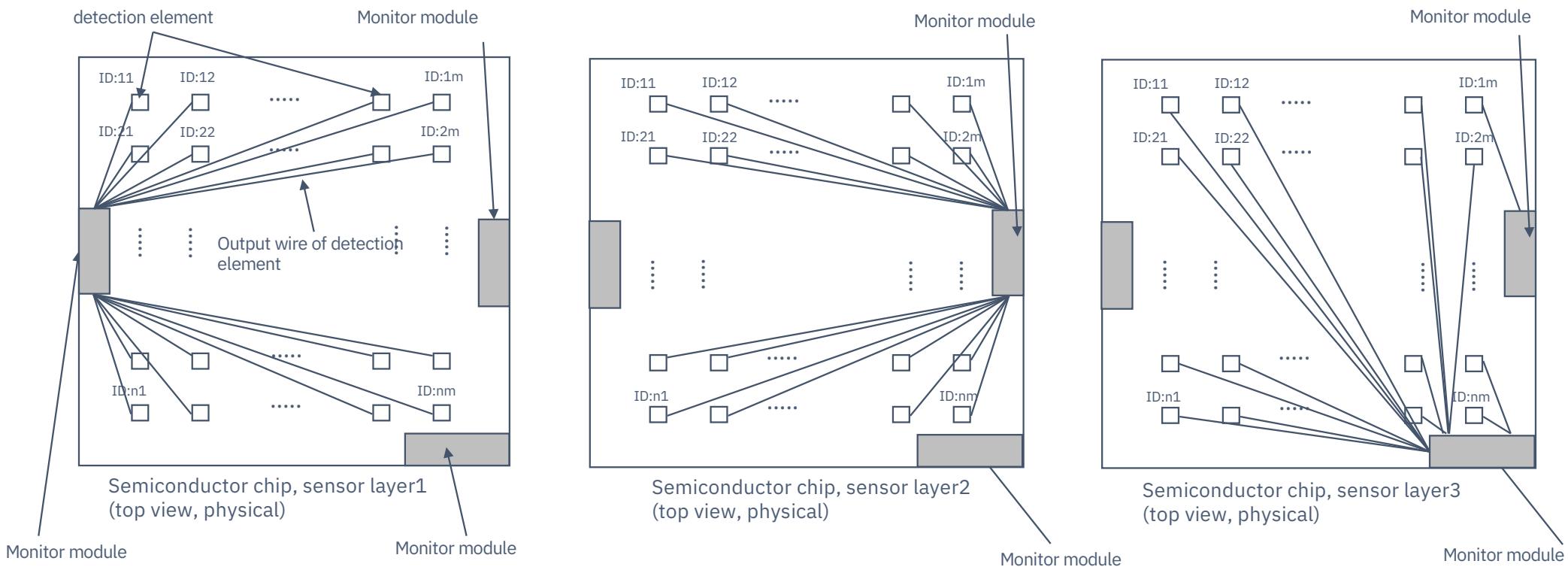

# "Silicon Heartbeat" - Detecting neutron showers and heavy-ion particle collisions

- The data inversion cycle is 1.0Hz, very slowly beating

- Implemented through logic design and placement and routing design.

- Independent of technology node and manufacturing process.

## Core ideas

- A small circuit and clock for bit-flip detection are prepared.

- A large number of the detection circuits are distributed on the chip.

- In order to identify the affected location, it is equipped with a circuit (register) that grasps the position, ID, and status of the detection circuits.

Circuit of a detection element

## Implementation Details - Detecting neutron showers and heavy-ion particle collisions

### To avoid single failure mode

- Monitor module(s) monitor output of detection elements

- Triple redundancy applied

- Parallel connection between detection elements and one or more Monitor module(s)

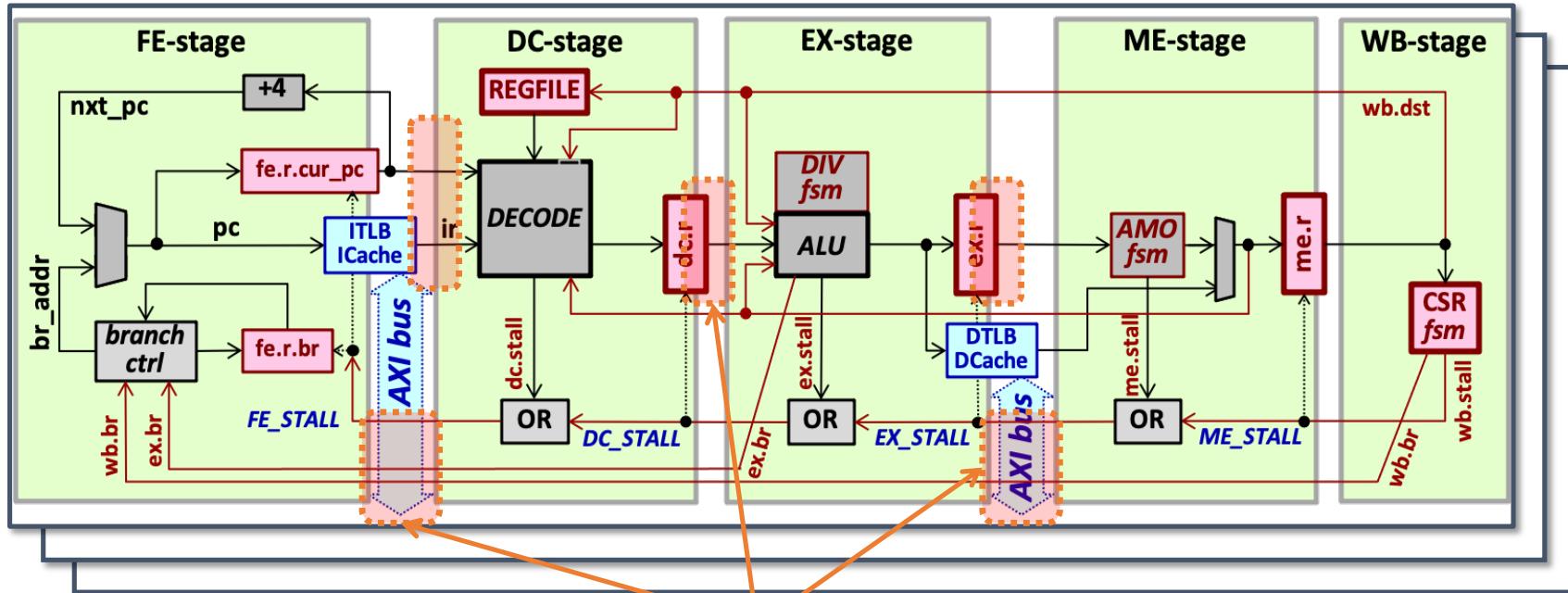

# RISC-V HD(High dependability) Processor

- **Triple-redundant RISC-V core:** Temporary fault detection via majority voting of internal redundant signals.

- **CRAM error detection:** If fault detection persists for multiple clock cycles, it is judged as a CRAM error and the faulty core's CRAM is rewritten (using ICAP).

- **FF Error:** Detected and automatically corrected by Latch circuit Error countermeasures.

- **Data RAM Error:** SRAM scrubbing - SW/OS cooperation.

- Fault area narrowing via **Silicon Heartbeat**.

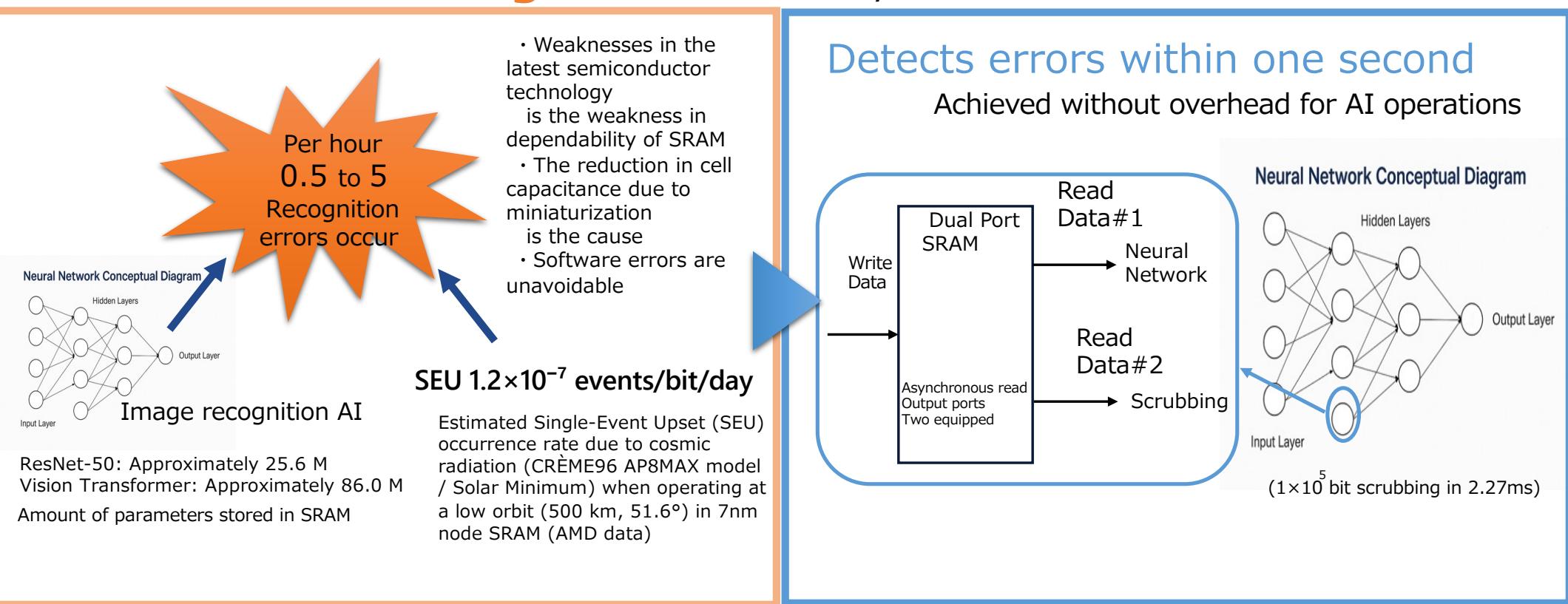

# Radiation Resistance – Memory Error Correction

## Overcomes weaknesses of the latest technology node

- Using off-the-shelf GPGPUs or AI accelerators as-is is **dangerous**

- SRAM and scrubbing mechanism adopted by DIOS

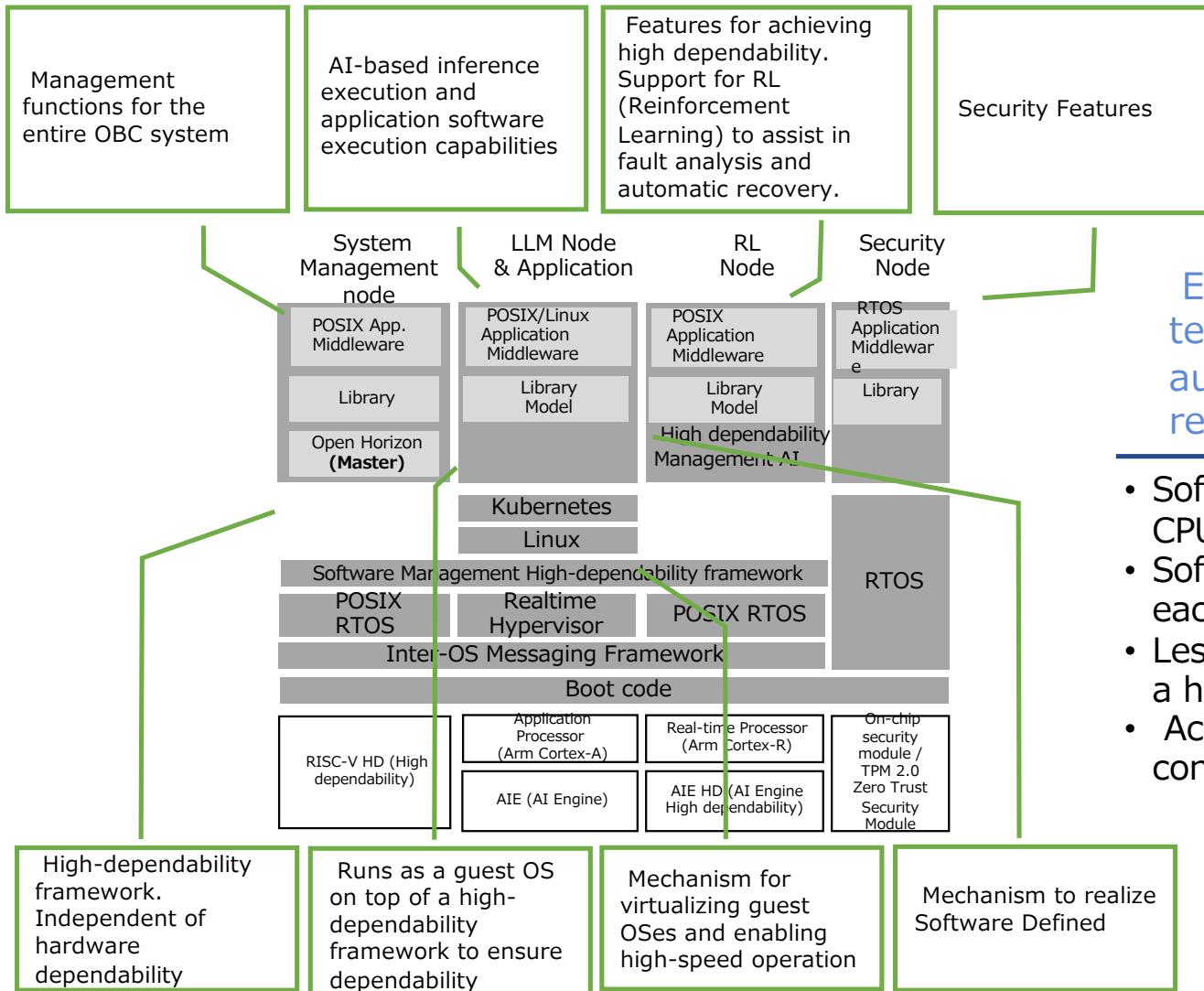

# DIOS Software architecture

Early adoption of high-dependability technologies meeting next-generation autonomous vehicle functional safety requirements (ISO 26262)

- Software is dedicatedly assigned to individual CPUs.

- Software running on CPUs or accelerators is each loosely coupled.

- Less reliable Linux runs as a guest OS on top of a high-dependability framework

- Achieving "Software Defined" through container technology (Kubernetes)

# To realize autonomous systems AI autonomously controls dependability and energy consumption

## Types of Damage Recovery in DIOS

Selecting the appropriate damage recovery from unpredictable cosmic ray-induced errors with many timing variations and dynamically changing hardware resource states

- Reset of specific IP core: 10 nsec

- Re-execution of specific software (function): Several microseconds until re-execution begins

- OS Reload: 5 to 10 sec

- System reset: 10 sec

- Disabling specific IP cores: Several microseconds until disabled

- Disabling specific memory and specific memory regions: Several microseconds until disabled

- FPGA restart: Several milliseconds

- IP core latch circuit reload: Several milliseconds

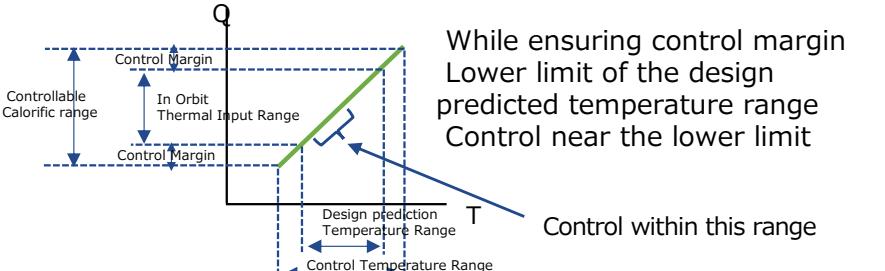

## Thermal Control in the Core Unit

Using AI to analyze data obtained from power consumption (current values) and temperature (temperature sensors), the Core Unit proactively controls heat generation to ensure it always remains below the TDP using the following three functions:

- Function to reduce energy consumption by lowering the clock frequency

- Clock gating function

- Power gating function

## Challenges in Establishing Autonomy

Dynamically changing large amounts of hardware resources

Control the status of

### Objective Function

- Minimize energy consumption = heat generation

- Maximize computational performance

- Maximize system lifetime

### Variables

- OBC x10

- Application CPU x80

- Real-time control CPU x100

- RISC-V HD x10

- AI Engine x10

- AI Engine HD x10

All of the above: Clock frequency, clock supply, power supply, reset, and function stop

### Constraints

- Radiation error types and frequency

- MTBF / MTTR

- Response time

- Maximum energy consumption

- Maximum Heat Generation

- Thermal Control Limit Ranges

- Workload size

Mathematical optimization is small-scale but becomes complex due to dynamic changes

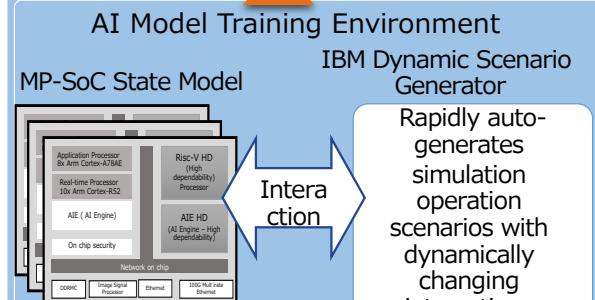

## Approach to AI Orchestration

Using reinforcement learning and mathematical optimization

Application of AI Orchestration Technology

The AI Engine HD and RL node software suite enables highly reliable and high-speed control of the status of each hardware resource

Reinforcement Learning (Deep Reinforcement Learning)

AI Model

1. Automatically generates unintended (unpredictable) simulation scenarios. Complies with autonomous vehicle safety standard SOTIF-ISO/PAS21448.

2. Achieves high-speed automatic generation with low computational cost by incorporating bio-inspired Active Matter technology into dynamic interaction calculations

# Conclusion

## Full-Stack approach for high-dependability

### ● High-dependability hardware

---

- High-dependability CPU: RISC-V HD (High Dependability)

- High-dependability AI Accelerator: AI Engine HD

- MP-SoC (Multi-Processor System on a Chip) configuration suitable for both application and real-time uses

### ● High-dependability Software

---

- Virtualized Linux running on a high-dependability framework

- High-dependability real-time OS and real-time hypervisor

- Early adoption of high-dependability technology meeting next-generation autonomous vehicle functional safety requirements (ISO 26262)

### ● AI-Based System Resource Control

---

- Achieves high dependability, high energy efficiency, and low heat dissipation through AI-based control of dependability functions and system resource management

- Utilization of reinforcement learning-based AI

- Integrated control via autonomous AI - Operational range restricted for safety assurance

# Next Step

- Development of a prototype system.

- Functional verification and radiation resistance measurement on the ground and in orbit.

- Calculation of high-dependability coverage and verification of validity.

End of Package