D\_RD\_17 Development of high-speed detector readout system

S. YAMADA (KEK) AND D. CHARLET (IJCLAB)

Contact address : <u>satoru.yamada@kek.jp</u> charlet@lal.in2p3.fr

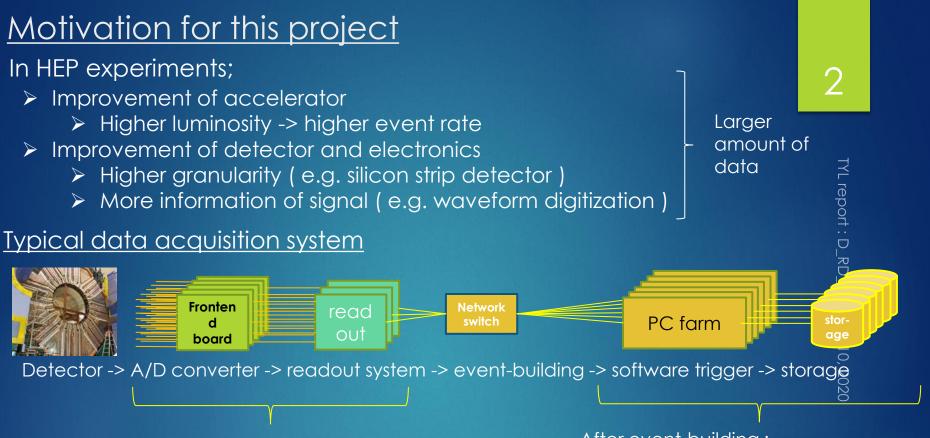

Scalability is not so good.

After event-building : Scalable system by parallel processing

Readout system could be the bottleneck of DAQ system.

-> development of high-speed readout system is important to improve the total throughput of system

Goal of the project : Upgrade the readout system of the Belle II experiment

## The Belle II experiment

Search for new physics beyond the Standard Model via high precision measurement with high statistics samples of B/D/tau decays.

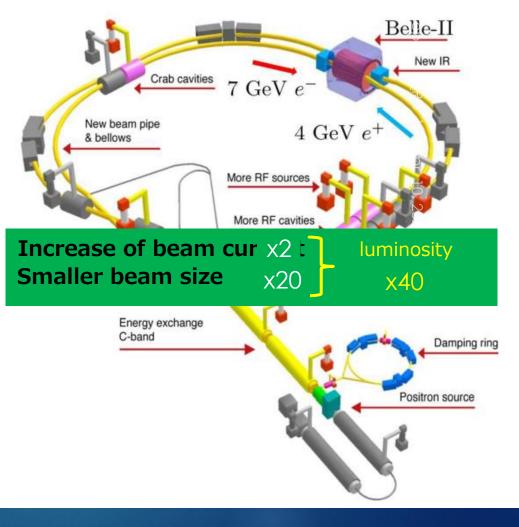

#### SuperKEKB accelerator

- Designed luminosity: 40times as large as KEKB

- 50 ab<sup>-1</sup> in 10 years

(cf. 1ab<sup>-1</sup> @ Belle experiment)

Belle II collaboration : ~1000 collaborators from 26 countries/regions

3

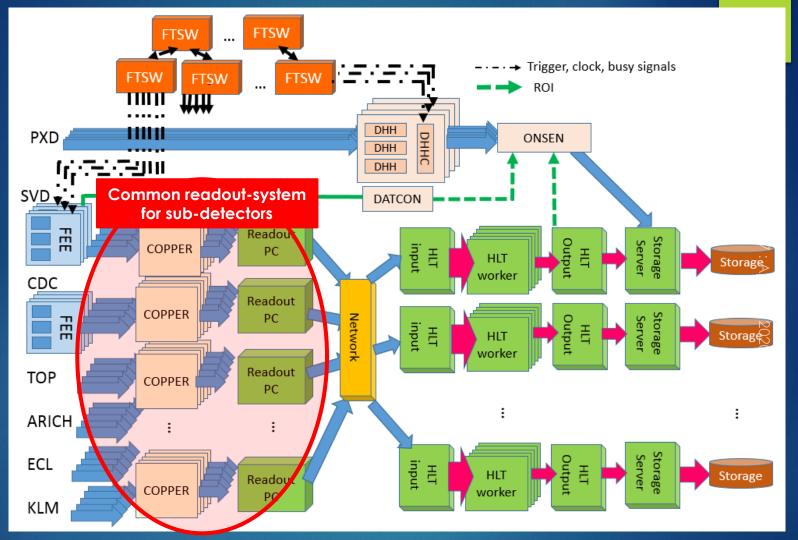

## READOUT SYSTEM IN BELLE II DAQ

Readout data from FEE(Front-End Electronics)s for six sub-detectors other than Pixel detector

Formatting, data-checking and partial event-building should be done

<u>Issues to be considered for the current readout system</u>

5

TYL report : D

#### Difficulty in maintenance during the entire Belle-II experiment period

- Four different boards, COPPER(main VME9U board) and its three daughter cards, should be taken care of.

- > The number of discontinued parts is increasing.

#### Limitation in the improvement of performance of DAQ

Apr. 10 A. Bottlenecks of the current COPPER readout system CPU usage on COPPER About 60% COPPER-CPU is used at "30kHz L1 trigger rate with 1kB event size/COPPER" (=Belle II DAQ target value) Data transfer speed from a COPPER board IGbps/COPPER (Gigabit ethernet) B. Bottleneck due to network output of ROPC IGbps/COPPER (Gigabit ethernet) We need to upgrade the readout system when \* Iuminosity of SuperKEKB exceeds expectations. \* Higher background than expected Lower threshold of L1 trigger is used or trigger-less DAQ is realized.

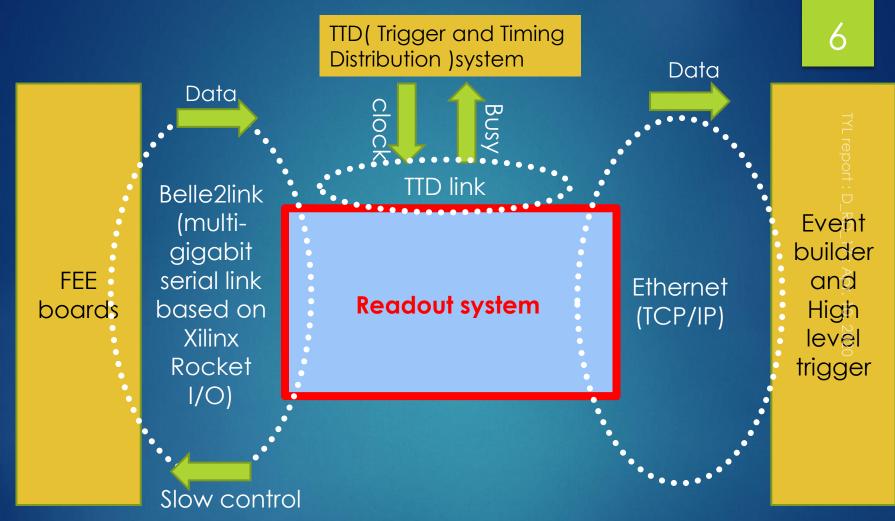

### New system needs to keep interface with the others

Three interfaces with the other part of the DAQ system should be kept so that It does not require further modification of the other subsystems.

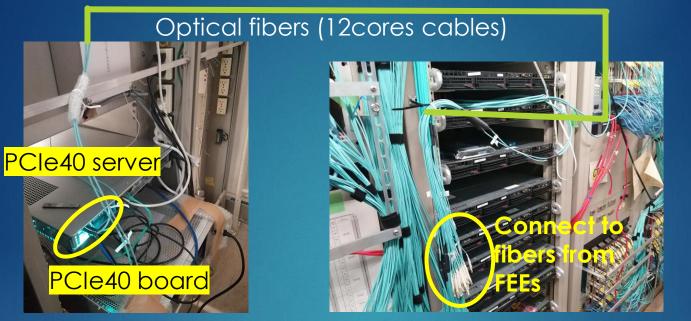

## PCIe40-board solution for the Belle II readout

Proposal based on PCIe40 boards used by ALICE and LHCb for their detector upgrades (full detector readout at 40 MHz and software trigger)

- Final hardware available and well tested at CERN

- Based on large Intel/Altera Arria 10 FPGA, with 48 bidirectionnal links

## <u>Manpower for the development and commissioning</u>

| item                                                               | people                                                           |  |

|--------------------------------------------------------------------|------------------------------------------------------------------|--|

| PCIe40 firmware and driver software                                | D.Charlet , P.Robbe, ,E.Jules , E.Plaige<br>,M.Taurigna (IJCLab) |  |

| Slow control firmware/library                                      | Q. Zhou (KEK), H. Purwar(Hawaii) (+ P. Robbe and D. Charlet )    |  |

| User logic part of FW, DAQ software on readout PC                  | S. Yamada (KEK) (+ P. Robbe and D.<br>Charlet )                  |  |

| FW development of TTD interface in PCIe40                          | <b>T. Kunigo, M. Nakao(KEK)</b> ,<br>H.Purwar(Hawaii)            |  |

| Readout test and commissioning                                     | <b>Q. Zhou, S. Yamada(KEK)</b> , H. Purwar(Hawaii)               |  |

| Slow control software upgrade for<br>handling larger # of channels | O. Hartbrich (Hawaii), <b>S. Yamada,</b><br><b>Q.Zhou(KEK)</b>   |  |

- PCIe40 related firmware and software (e.g. Belle2link, PCIexpress interface, driver software etc.) -> IJCLab experts

- Implement of Belle II DAQ functionalities ( data-formatting, checking ,slow control etc.) -> KEK DAQ group + UH group

- Test and commissioning : KEK DAQ group + UH UH group

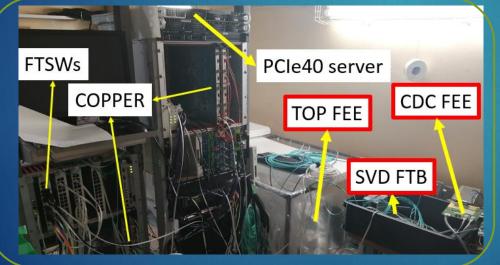

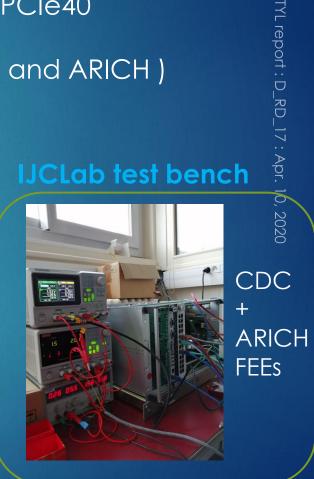

## Test setups in KEK and IJCLab

- There are three test benches for new PCIe40 readout system.

- FEEs of sub-detectors (TOP, CDC, SVD and ARICH) can be connected.

#### **KEK Tsukuba Hall test bench**

#### IJCLab test bench

## READOUT TEST AT KEK

### Example of read-out data

TOP readout test with 4 FEEs ( The FEEs were not configured yet.)

00000034 7f7f0001 02c13f00 0000001e 27b853a7 5e269114 1a160060 00000000 0000000a ffaa0100 27b872f0 0401a04a 00000005 013a2145 ffff011e 00000a00 001eb623 ff554103 0000000a ffaa0101 24b372c0 0401a058 0000005 013a2145 ffff011e 00000a00 001e4075 ff554202 0000000a ffaa0002 27b872c0 0401a029 0000005 013a2145 ffff011e 00000a00 001e4075 ff554302 0000000a ffaa0003 27b872b0 0401a067 0000005 013a2145 ffff011e 00000a00 001e452d ff554401 7fff0000 7fff0004 7fff0005 7fff0006 7fff0007 7fff0008 7fff0009 7fff000a

Currently just dumping data from PCIExpress to PC's disk.

CRC check/Unpacker software's check needs to be done

Data

**FEEs**

from 4

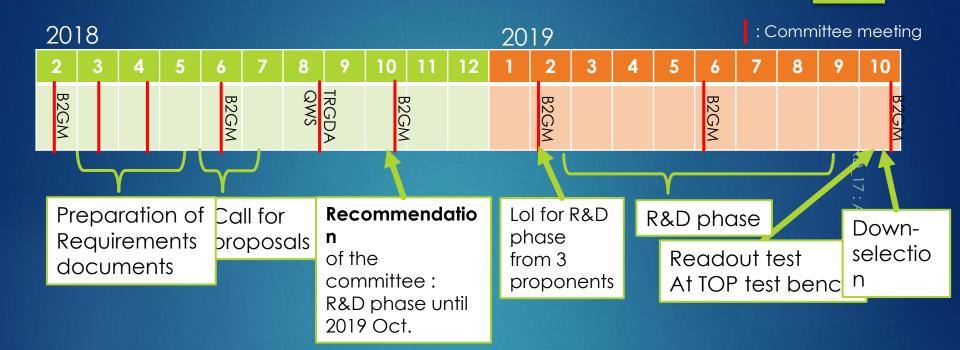

### PCIe40 proposal was selected by Belle II collaboration in Oct. 2019

> The committee was formed to make recommendation for the upgrade

- Call for proposals for the DAQ upgrade to gather collaboration-wide resources and expertise

- A simple readout test was performed by proponents at TOP(a PID detector of the Belle II) test bench to demonstrate the capability of new systems.

- PCIe40 proposal was selected by the Belle II management.

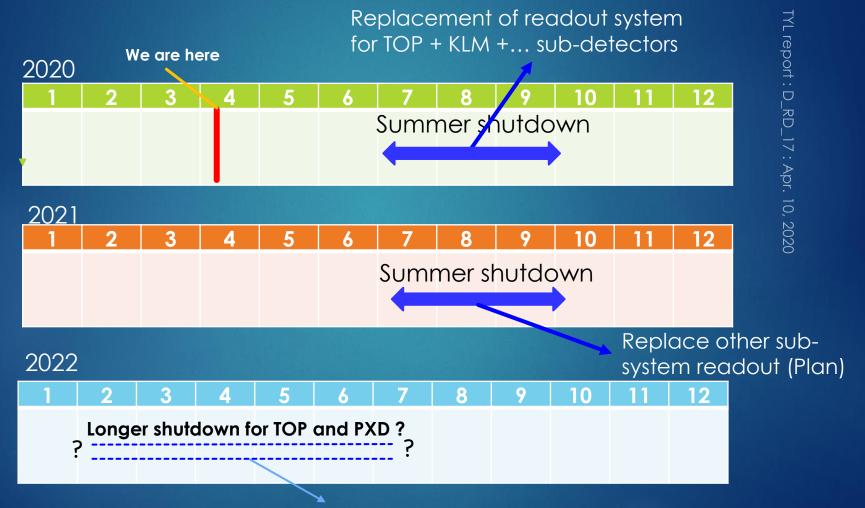

### Installation plan

Installation will be done during accelerator shutdown period

Running the current system+PCIe40 system in parallel

(The current readout system will be in hot-standby operation)

Contingency for installation

## Current Members of the D\_RD\_17 project

| French group            |            | Japanese group |              |  |

|-------------------------|------------|----------------|--------------|--|

| Name                    | Laboratory | Name           | Laboratory   |  |

| Daniel Charlet          | IJCLab     | Satoru Yamada  | KEK          |  |

| Christophe<br>Beigbeder | IJCLab     | Ryosuke Itoh   | KEK          |  |

| Eric Jules              | IJCLab     | Mikhiko Nakao  | KEK          |  |

| Emi Kou                 | IJCLab     | Qidong Zhou    | Nagoya univ. |  |

| Francois Le Diberder    | IJCLab     | Takuto Kunigo  | KEK          |  |

| Eric Plaige             | IJCLab     |                |              |  |

| Patrick Robbe           | IJCLab     |                |              |  |

| Monique Taurigna        | IJCLab     |                |              |  |

TYL report : D\_RD\_17 : Apr. 10, 2020

#### Collaborative efforts are ongoing between IJCLab and KEK

#### Belle II DAQ upgrade project

#### KEK members visited in Feb. 2020

IJCLab membersImage: Second secon

4

TL report

KEK

IJCLab

# Summary

- High-speed readout system is one of the key component in HEP DAQ system to keep up with the improvement of accelerator and detector.

- The Belle II experiment started operation in February, 2018 and our target is to upgrade its readout system.

- PCIe40 board-based solution was proposed to the Belle II collaboration and was approved in Oct. 2019.

- Develoepment of firmware and software are ongoing and successfully read data from front-end electronics of Belle II sub-detectors at a test bench.

- Partial replacement of the Belle II readout system is planned in the summer of 2020.

15