#### 令和5年11月23日 Flavor Physics Workshop 2023

# J-PARC muon g-2/EDM実験のための 2枚のFPGAを搭載した フロントエンド基板の開発

**岡村麗矢**<sup>B</sup>, 池野正弘<sup>E, M</sup>, 上野一樹<sup>I, M</sup>, 梅林恵祐<sup>J</sup>, 岡崎佑太<sup>E, M</sup>, 小川真治<sup>K, M</sup>, 川越清以<sup>J</sup>, 岸下徹一<sup>E, M</sup>, 久米達哉<sup>G</sup>, 高力孝<sup>E, M</sup>, 齊藤直人<sup>E</sup>, 佐々木修<sup>E, M</sup>, 佐藤太希<sup>H</sup>, 佐藤伸彦<sup>G</sup>, 佐藤優太郎<sup>C, M</sup>, 庄子正剛<sup>E, M</sup>, 末原大幹<sup>J, M</sup>, 鈴木純一<sup>E</sup>, 須田利美<sup>A</sup>, 清野義敬<sup>D</sup>, 千代浩司<sup>E, M</sup>, 高富俊和<sup>G</sup>, 田中真伸<sup>E, M</sup>, 東城順治<sup>J, M</sup>, 西村昇一郎<sup>F, M</sup>, 藤田陽一<sup>E, M</sup>, 本多佑記<sup>A</sup>, 本多良太郎<sup>E, M</sup>, 水取雅登<sup>J</sup>, 三部勉<sup>E, M</sup>, 山岡広<sup>E</sup>, 山中隆志<sup>L, M</sup>, 矢村昂暉<sup>B</sup>, 吉岡瑞樹<sup>K, M</sup>, 他J-PARC muon g-2/EDMコラボレーション

東北大電子光<sup>A</sup>, **新大自<sup>B</sup>**,新大理<sup>C</sup>,富山高専<sup>D</sup>, KEK素核研<sup>E</sup>, KEK物構研<sup>F</sup>, KEK機械工学セ<sup>G</sup>,東大理<sup>H</sup>,阪大理<sup>I</sup>,九大理<sup>J</sup>,九大RCAPP<sup>K</sup>,九大基<sup>L</sup>,Open-It<sup>M</sup>

# J-PARC muon g-2/EDM実験について

### ミューオンg-2について

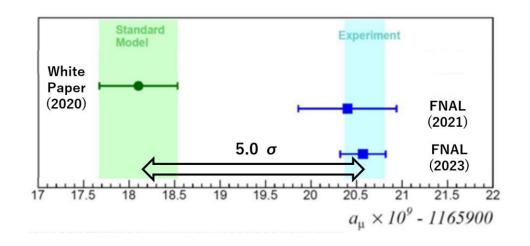

- FNALの実験で測定されたミューオンの 異常磁気能率( $\mathbf{g-2}$ )の値は、理論予想値と  $5.0 \sigma$  ずれている。

- ▶標準理論を超えた物理を示唆

- J-PARC muon g-2/EDM実験はミューオンの

- > g-2

- ➤電気双極子能率(EDM)

を先行実験とは**異なる方法**で測定。

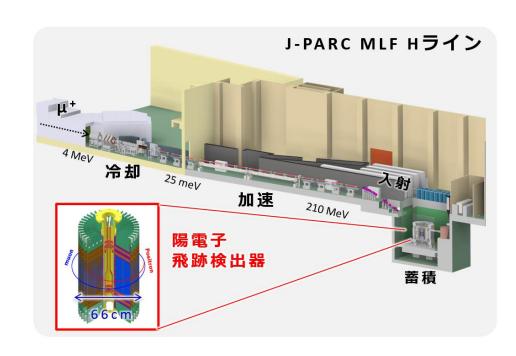

### J-PARC muon g-2/EDM実験の特徴

- エミッタンスの小さいミューオンビーム

- 三次元らせん入射

- 陽電子飛跡検出器による崩壊陽電子の 飛跡の再構成

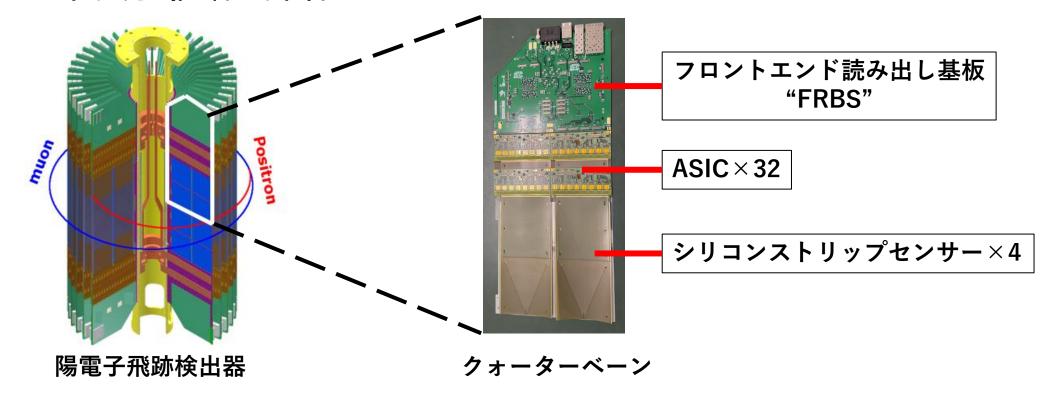

## 陽電子飛跡検出器

- センターポールに"ベーン"を放射状に配置。

- ベーンはさらに4つのクォーターベーンから構成され、検出器全体で160枚になる。

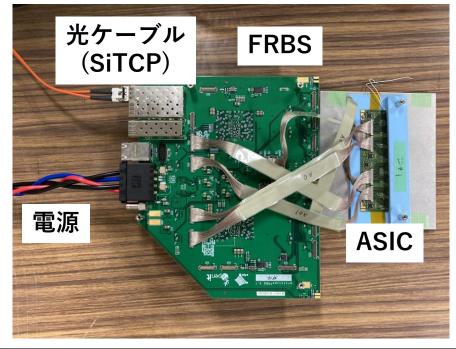

- クォーターベーンのフロントエンド読み出し基板を**FRBS**という。

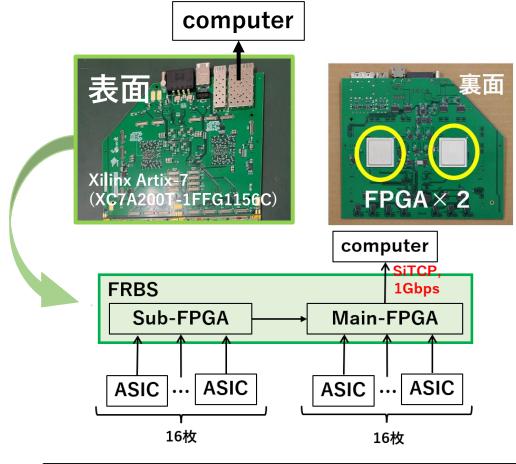

## フロントエンド読み出し基板"FRBS"

#### FRBSについて

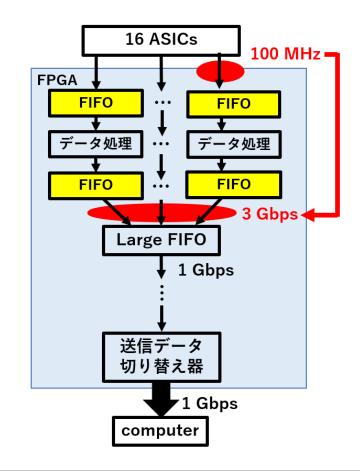

- 32 枚のASICの信号を処理するために FRBSには2つのFPGAを搭載

- 空間の制約上、FPGA からコンピュータへ データ転送するためのポートは1つ

- ➤ Main-FPGAのみがコンピュータと接続

- Sub-FPGAで処理したデータは Main-FPGAを経由しコンピュータへ送信

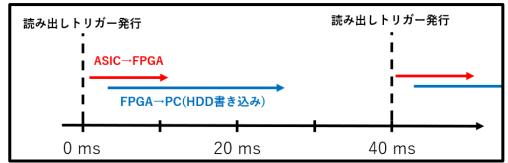

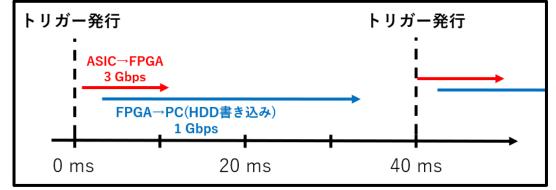

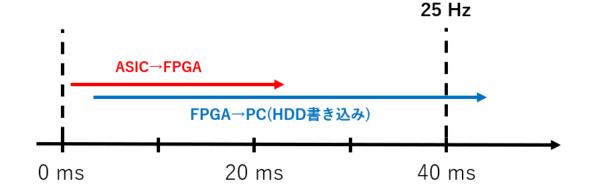

- J-PARC のビームの繰り返しレート: 25 Hz ▶トリガー間隔以内に読み出す必要がある。

#### 研究課題

FPGA間で通信して、2つのFPGAの データをトリガー間隔以内に コンピュータへ送信する。

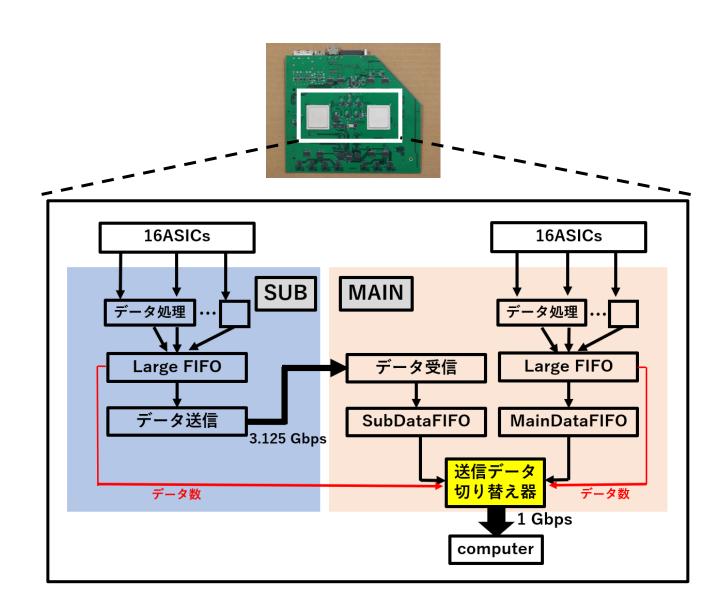

### ファームウェアの概要

- ① ASICからのデジタル信号をデータ フォーマットに従ってまとめる ➤ ヒット時刻、チャンネル番号

- ② ギガビットトランシーバ (GTP)を使用してFPGA間で データを送受信

- ➤ 通信プロトコルは8b10b

- ➤ 20 bit幅で3.125Gbpsの通信

- ➤ FPGA間の通信が安定している ことはIBERTで確認済み

- ③ 送信データの切り替え

- メインとサブのデータ数を比較し、多い方を優先して送信する。

## 2つのFPGAの並列読み出し試験

### 試験目的

• 想定されるヒットレートを安定して読み出せるか

### 試験方法

- ① ASICに疑似データを書き込む

- ② FRBSからASICに読み出しトリガーを送り、 ASICのデータを決められた時間読み出す

- ③ 読み出したヒット数から読み出しが成功したかを判定

### 読み出し成功の定義

▶ ASICに書き込んだ疑似データのヒット数と 読み出したヒット数がすべてのイベントで 一致していたら"読み出し成功"とした。

```

#Active ASIC :

start to readout from 1 boards during 600 sec.

event_number = 0 : Hit_Main = 361044 : Hit_Sub = 359844 : Hit_all = 720888

event_number = 1 : Hit_Main = 361044 : Hit_Sub = 359844 : Hit_all = 720888

event_number = 2 : Hit_Main = 361044 : Hit_Sub = 359844 : Hit_all = 720888

event_number = 3 : Hit_Main = 361044 : Hit_Sub = 359844 : Hit_all = 720888

event_number = 4 : Hit_Main = 361044 : Hit_Sub = 359844 : Hit_all = 720888

event_number = 5 : Hit_Main = 361044 : Hit_Sub = 359844 : Hit_all = 720888

event_number = 6 : Hit_Main = 361044 : Hit_Sub = 359844 : Hit_all = 720888

event_number = 7 : Hit_Main = 361044 : Hit_Sub = 359844 : Hit_all = 720888

event_number = 8 : Hit_Main = 361044 : Hit_Sub = 359844 : Hit_all = 720888

event_number = 9 : Hit_Main = 361044 : Hit_Sub = 359844 : Hit_all = 720888

event_number = 10 : Hit_Main = 361044 : Hit_Sub = 359844 : Hit_all = 720888

event_number = 11 : Hit_Main = 361044 : Hit_Sub = 359844 : Hit_all = 720888

event_number = 12 : Hit_Main = 361044 : Hit_Sub = 359844 : Hit_all = 720888

event number = 13 : Hit Main = 361044 : Hit Sub = 359844 : Hit all = 720888

event_number = 14 : Hit_Main = 361044 : Hit_Sub = 359844 : Hit_all = 720888

event_number = 15 : Hit_Main = 361044 : Hit_Sub = 359844 : Hit_all = 720888

event number = 16 : Hit Main = 361044 : Hit Sub = 359844 : Hit all = 720888

event number = 17 : Hit Main = 361044 : Hit Sub = 359844 : Hit all = 720888

```

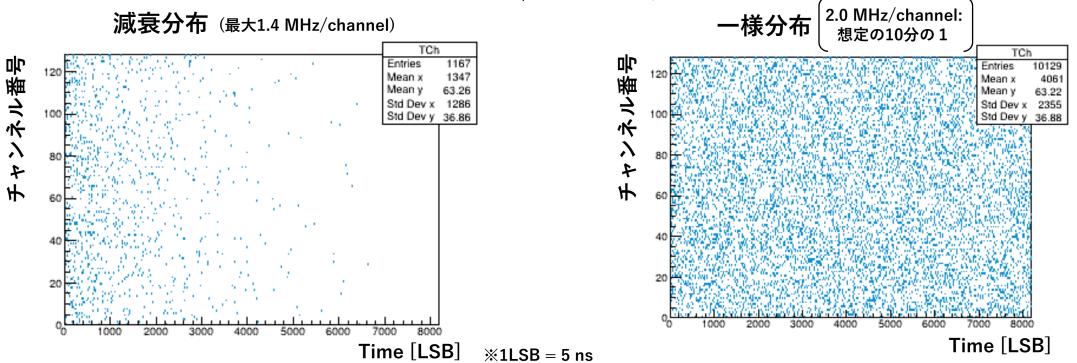

# 使用した疑似データ

- 指定したヒットレートになるような疑似データをASIC に書き込む。

- 2 つの使用環境を想定して、2 種類の時間分布のヒットデータで試験した。

- ① 実験本番を想定:指数関数による減衰分布

- ▶想定されるヒット数:約38,000ヒット/FRBS

- ② しきい値スキャンを想定:一様分布

▶想定される最大ヒット数:約720,000ヒット/FRBS

### 読み出し結果

### 実験本番を想定した減衰分布の読み出し結果

読み出し時間:300秒

| 書き込んだヒット数 | 301,253 | 322,553 |

|-----------|---------|---------|

| 結果        | 成功      | 失敗      |

• 想定されるヒット数を上回るヒット数で読み出し成功。

・ 実験本番でも安定して読み出せる。

>> 想定されるヒット数(38,000)

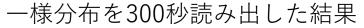

### しきい値スキャンを想定した一様分布の読み出し結果

読み出し時間:300秒

| 書き込んだヒット数 | 431,089 | 466,922 |

|-----------|---------|---------|

| 結果        | 成功      | 失敗      |

想定される最大ヒット数には 届かなかった。

< 想定される最大ヒット数 (720,000)

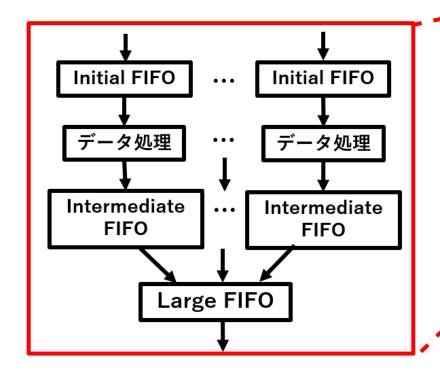

### 読み出し失敗の原因

- オーバーフローしているのはLarge FIFOの上流側のFIFO。

- 各ASICで並列に処理していたデータをLarge FIFO に 集約する部分がボトルネックになっている。

### 対策

- FIFOの容量を増やす

- ▶ 現状、想定データの3.3 %分しか保存できない。

- ② ASICからFPGAへのデータ転送レートを抑える

Large FIFOに入るデータレート =  $\frac{(ヒット数)\times(1 ヒット当たりのデータ量)}{\text{FPGAがASIC}}$ のデータを読み出す時間

➤ ASIC の読み出しクロック周波数を遅くして、 ASIC からFPGA へのデータ転送レートを調節する。

#### 72 万ヒット読み出す場合

# ① FIFOの改善

これまでは、Large FIFOの容量を大きく 取っていたが、1 ASICあたりの実効的な FIFOの深さが一番深くなるように最適化した。 BRAM使用率:メインFPGA90 %

サブFPGA84%

|                                                    | 修正前                       | 修正後                        |

|----------------------------------------------------|---------------------------|----------------------------|

| Initial FIFO                                       | 256                       | 1024                       |

| Intermediate FIFO                                  | 512                       | 4096                       |

| Large FIFO                                         | 65536                     | 16384                      |

| 1ASICあたりの<br>実効的なFIFOの深さ<br>(Intermediate + Large) | 512+4096<br>= <b>4608</b> | 4096+1024<br>= <b>5120</b> |

16 ASICs

Large FIFO

送信データ 切り替え器

computer

FIFO 3 Gbps

1 Gbps

1 Gbps

# ① FIFOの改善結果

- Initial FIFOのみを修正して試験した。

- ▶深さ256→深さ1024に変更

• 16 ASIC接続する場合は、Intermediate FIFOの修正も、 容量が増えるので読み出せるヒット数も増えることが期待できる。

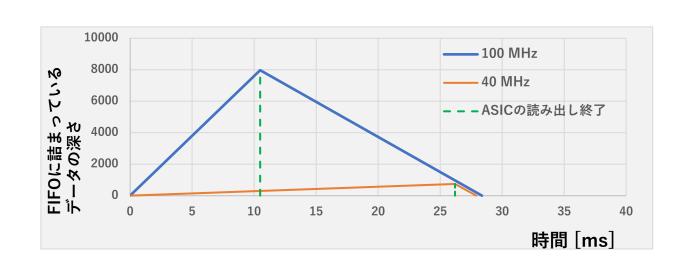

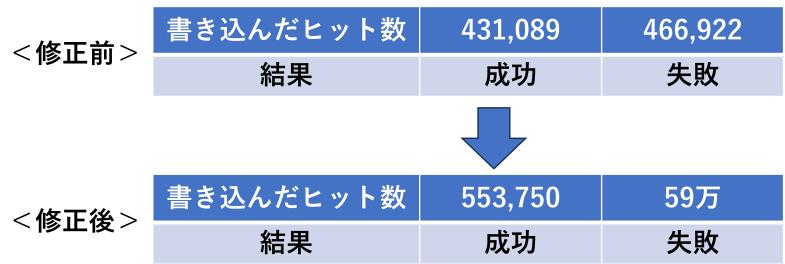

# ②読み出しクロック周波数の最適化("トロワロサット゚)

### 試験方法

- FIFOを最適化したFWから、読み出しクロック 周波数のみを段階的に変更していき、読み出し クロック周波数と読み出せるヒット数の関係を調べた。

- また、HDDへの書き込みがボトルネックに なっていることが分かったので、この試験では HDD書き込みを停止して試験した。

### 結果

- 40~100 MHzの間では、クロック周波数を下げるほど、読み出し数が増える傾向にある。

- ・読み出しクロック周波数を40MHz以下にすることで、 想定されるヒット数を読み出すことができた。

- 読み出しクロック周波数が40 MHz の場合の、 データ転送レート約0.88 Gbps。

- ▶理論上限値(SiTCP 1Gbps) のボトルネックが 見えていると思われる。

#

- 実験本番ではHDD書き込みを行うため、HDD書き込みありの状態で再度試験を行った。

- HDD書き込みありの試験ではHDD書き込み無しの状態で成績が良かった32~40 MHzの中で、読み出し時間が一番短い40 MHzのクロック周波数のFWを使用することにした。

- ① トリガーレート25 Hzで何ヒットまで読み出せるか。

- ② しきい値スキャンで想定される72万ヒットは トリガーレート何Hzで読み出せるか。

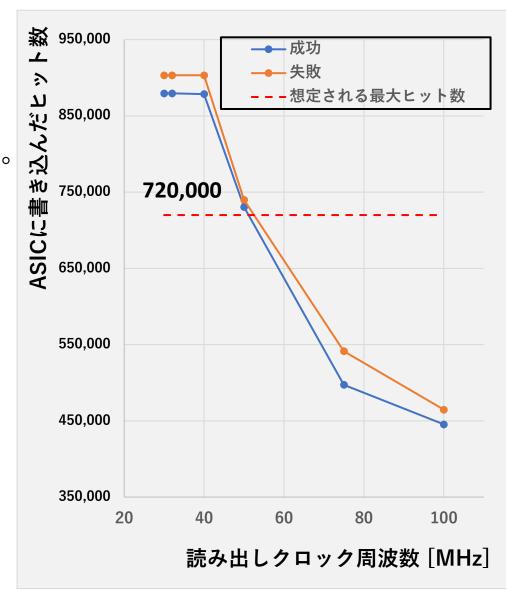

### トリガーレート25 Hzで読み出せるヒット数

• 設計値通りのトリガーレート25 Hzでは、どのくらいのヒット数まで 読み出せるのかを調べた。

読み出しクロック周波数:40 MHz 読み出し時間:600秒

読み出しが25 Hzに間に 合わなかったイベント数

- 50 万ヒットまでは読み出すことができた。

- しきい値スキャンで想定される72万ヒットは87.8%の読み出し成功率となった。

### 72万ヒットを読み出せるトリガーレートの調査

- しきい値スキャンで想定される

72万ヒットは、トリガーレート25 Hzでは安定して、読み出せないことが分かった。

▶40 ms以内に読み出しが終わらないため

- 読み出し間隔を広くすることで解決する。

・結論:15 Hzであれば想定される 最大ヒット数72 万ヒットを 読み出すことができる。

読み出しクロック周波数:40 MHz 読み出し時間:600秒

| トリガー<br>レート[Hz] | 読み出した<br>イベント数 | 読み出しに間に合わ<br>なかったイベント数 |

|-----------------|----------------|------------------------|

| 20              | 11348          | 374                    |

| 15              | 9066           | 0                      |

| 10              | 6092           | 0                      |

| 5               | 2999           | 0                      |

# まとめ・今後

- J-PARC muon g-2/EDM 実験で使用する検出器の フロントエンド読み出し基板"FRBS"を開発している。

- FPGA間でデータを送受信し、2枚のFPGAのデータをコンピュータへ送信する FPGAファームウェアを開発。

- 疑似データのデータレートを変えながら読み出し試験を行った。

- ・減衰分布の読み出し試験では実験本番で想定されるヒット数を読みだせることを確認。

- 一様分布の読み出し試験ではしきい値スキャンで想定されるヒット数の読み出しが、 できなかったため、FWを改善した。

- ▶FIFO の配置を最適化し、ASIC→FPGAの読み出しクロック周波数を変更した。

- HDD書き込みを停止して試験した結果、読み出しクロック周波数は40 MHzが最適。

- FWを改善した状態でトリガーレートを15 Hzに変更すると、 しきい値スキャンで想定される最大ヒット数を読み出せることが確認できた。

- 今後は、複数のHDDに書き込む試験を行う予定。

- また、磁場中にFRBSを入れて、実験本番に近い環境で動作試験を行う。

# Back up

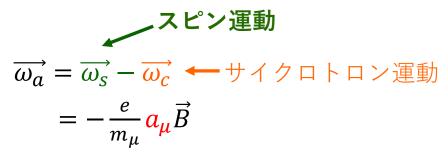

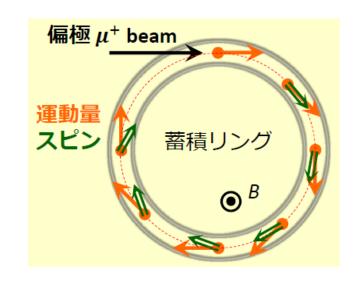

# ミューオンg-2の測定方法

• 磁気双極子能率の係数をg因子と呼ぶ。 2からのずれを異常磁気能率 $a_{\mu}$ と定義する。

$$a_{\mu} \equiv \frac{g-2}{2}$$

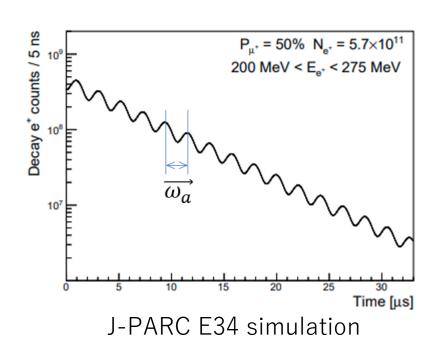

• g-2は異常歳差運動を用いて調べる。

- 異常歳差運動の周期とミューオンが感じた磁場を 測定することでmuon g-2( $a_{\mu}$ )を決定する。

- $\overrightarrow{\omega_a}$ はwiggle plotから求められる。

- J-PARCの実験では、崩壊陽電子の飛跡を再構成して ミューオンの崩壊時刻を求める。

- ▶陽電子飛跡検出器を使用する。

### 1ch当たりの平均ヒット数

• ミューオン崩壊によるヒット数の減衰を考慮する。

$$N = \int_{0}^{40.96 \times 10^{-6}} 1.4 \times 10^{6} \times \exp\left(-\frac{t}{\gamma\tau}\right) dt$$

$$N \sim 1.4 \times 10^{6} \int_{0}^{\infty} \exp\left(-\frac{t}{\gamma\tau}\right) dt$$

$$N = 1.4 \times 10^{6} \left[ (-\gamma\tau) \exp\left(-\frac{t}{\gamma\tau}\right) \right]_{0}^{\infty}$$

$$N = 1.4 \times 10^{6} \times \gamma\tau\{0 + 1\}$$

$$N = 1.4 \times 10^{6} \times 3.010290522 \times 2.1969811 \times 10^{-6}$$

$$N = 9.258971935$$

### 実験本番・しきい値スキャン時に予想されるヒット数

### 実験本番時に想定されるヒット数

- 実験本番時は、ASICの1 ch当たりに約9.26回(最大ヒットレート1.4 MHz)のヒットがある。

- $9.26[hit/ch] \times 128[ch/ASIC] \times 32[ASIC/FRBS] = 37928 \approx 38000[hit/FRBS]$

### しきい値スキャンで想定されるヒット数

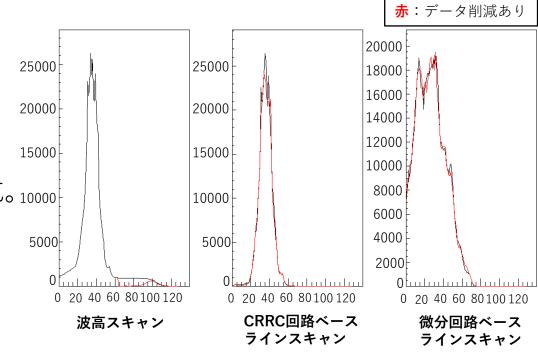

- 1ASICを使い、DACを変えながら以下を行った。

- ▶ CRRC回路でのテストパルスの波高スキャン

- ▶CRRC回路のベースラインスキャン

- ▶微分回路のベースラインスキャン

- 各スキャンでのDACと平均ヒット数でグラフを作成。<sub>10000</sub>

- 平均ヒット数はCRRCのベースラインスキャンで 最大となった。

- データ削減なし:26452 hit

- データ削減あり:24108 hit

• 実験本番では最大ヒット数は  $24108[hit/ASIC] \times 32[ASIC/FRBS] = 720704[hit/FRBS]$ 程になると予想される。

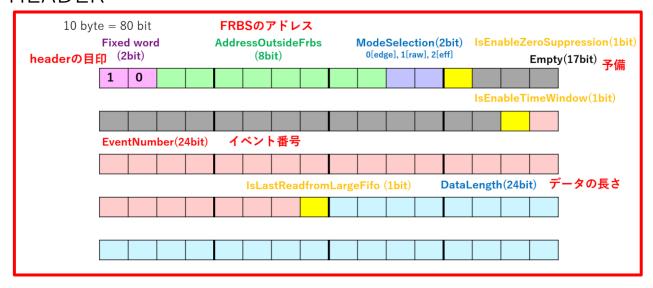

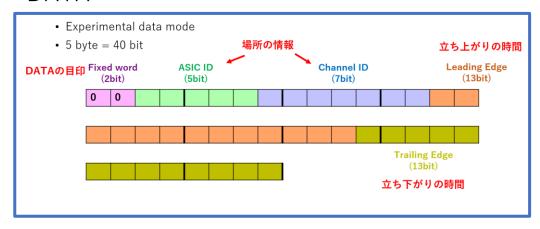

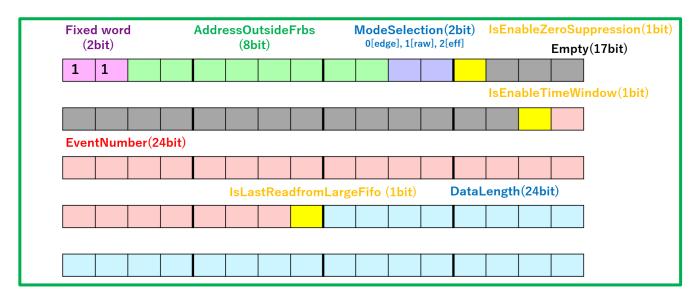

# データフォーマット

#### **HEADER**

#### DATA

#### **FOOTER**

センサーで、陽電子がヒットした時間と 場所の情報を紐づけるために HEADER、DATA、FOOTER というフォーマットでデータを送信する。

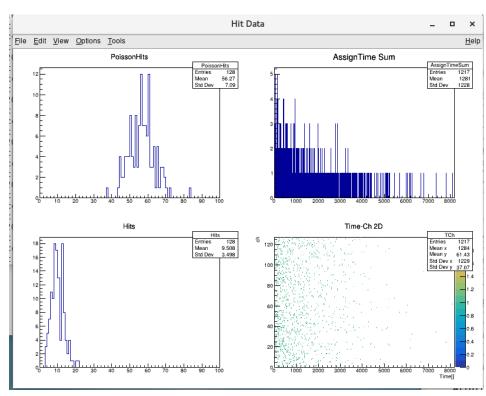

# データ生成プログラム動作内容

- ① ポアソン分布でヒットを示す乱数を生成して、その分だけ0~8191の間に割り振る。 ▶小さな確立で起こる事象が一定の時間内に発生するときの分布 ▶今回は、40.96 µ 秒の間に1.4MHzでヒットを割り振った

- ② ヒットが指数関数で減らなければいけないので、時間に伴って減少する指数関数と 乱数を割り振った時間ごとで比較する。

- ③ 乱数のほうが低ければヒットとして ヒストグラムに詰める。

# クロック周波数の変更によるFIFOの深さの見積もり